HANDBOOK

OF

AUTOMATION

COMPUTATION

AND

CONTROL

VOLUME 2

# HANDBOOK OF AUTOMATION, COMPUTATION, AND CONTROL

Volume 2

COMPUTERS AND DATA PROCESSING

NEW YORK • JOHN WILEY & SONS, INC.

London • Chapman & Hall, Limited

# HANDBOOK OF AUTOMATION, COMPUTATION, AND CONTROL

Volume 2

#### COMPUTERS AND DATA PROCESSING

Prepared by a Staff of Specialists

Edited by

EUGENE M. GRABBE

SIMON RAMO

DEAN E. WOOLDRIDGE

Thompson Ramo Wooldridge Inc. Los Angeles, California

Copyright @ 1959, by John Wiley & Sons, Inc.

All Rights Reserved. This book or any part thereof must not be reproduced in any form without the written permission of the publisher.

Library of Congress Catalog Card Number: 58-10800 Printed in the United States of America

### CONTRIBUTORS

- L. D. AMDAHL, Thompson Ramo Wooldridge Inc., Los Angeles, California (Chapter 17)

- C. E. AMMANN, American Airlines, New York City, New York (Chapter 9)

- I. L. AUERBACH, Auerbach Electronics Corporation, Narberth, Pennsylvania (Chapters 15 and 16)

- **G. A. BEKEY,** Space Technology Laboratories, Inc., Los Angeles, California (Chapter 23)

- E. E. BOLLES, Thompson Ramo Wooldridge Inc., Los Angeles, California (Co-Editor, Part D)

- R. BOSAK, System Development Corporation, Santa Monica, California (Chapter 9)

- J. K. BRIGDEN, Space Technology Laboratories, Inc., Los Angeles, California (Chapter 20)

- D. R. BROWN, The MITRE Corporation (formerly with Massachusetts Institute of Technology), Lexington, Massachusetts (Chapter 19)

- J. W. BUSBY, Alwac Corporation, New York City New York (Chapter 5)

- J. O. CAMPEAU, Litton Industries, Beverly Hills, California (Chapter 31)

- **R. G. CANNING,** Canning, Sisson and Associates, Los Angeles, California (Chapter 4)

- J. W. CARR, III, University of North Carolina (formerly with the University of Michigan), Chapel Hill, North Carolina (Chapter 2)

- R. B. CONN, Space Technology Laboratories, Inc., Los Angeles, California (Co-Editor, Part C)

- E. D. COWLES, The Detroit Edison Company, Detroit, Michigan (Chapter 8)

- **H. L. ENGEL,** Thompson Ramo Wooldridge Inc., Los Angeles, California (Chapter 18)

- E. M. GRABBE, Thompson Ramo Wooldridge Inc., Los Angeles, California (Co-Editor, Part D; Chapter 1)

- B. M. GORDON, EPSCO, Inc., Boston, Massachusetts (Chapter 29)

- W. J. KARPLUS, University of California at Los Angeles (Editor, Part E; Chapters 21, 25, and 27)

- W. KINDLE, Electronic Associates, Inc., El Segundo, California (Chapter 21)

- R. T. KOLL, Creole Petroleum Corporation, Caracas, Venezuela (Chapter 10)

- J. F. LA FONTAINE, EPSCO, Inc., Boston, Massachusetts (Chapter 29)

- H. T. LARSON, Aeronutronic Systems, Inc., Santa Ana, California (Co-Editor, Part C)

- C. T. LEONDES, University of California at Los Angeles (Chapter 28)

- H. S. LEVIN, Arthur Young & Company, New York City, New York (Chapter 7)

- **H. LOW,** Space Technology Laboratories, Inc., Los Angeles, California (Chapter 26)

- R. C. MACKEY, University of California at Los Angeles (Chapter 24)

- M. E. MARON, Thompson Ramo Wooldridge Inc., Los Angeles, California (Chapter 11)

- M. J. MENDELSON, Norden Division of United Aircraft Corporation, Gardena, California (Chapter 3)

- I. PFEFFER, Space Technology Laboratories, Inc., Los Angeles, California (Chapter 22)

- J. I. RAFFEL, Massachusetts Institute of Technology, Lincoln Laboratory, Lexington, Massachusetts (Chapter 19)

- C. W. SCHMIDT, Teleregister Corporation, Los Angeles, California (Chapter 9)

- **R. L. SISSON,** Canning, Sisson and Associates, Los Angeles, California (Chapter 4)

- N. H. TAYLOR, Itek Corporation, Boston, Massachusetts (formerly with Massachusetts Institute of Technology) (Chapter 14)

- H. TELLIER, General Electric Company, Richland, Washington (Chapter 8)

- E. TOMASH, Telemeter Magnetics, Inc., Los Angeles, California (Chapter 6)

- L. L. VAN OOSTEN, Allstate Insurance Company, Skokie, Illinois (Chapter 8)

- A. C. VANSELOW, The Franklin Life Insurance Company, Springfield, Illinois (Chapter 8)

- R. L. VAN WINKLE, The Franklin Life Insurance Company, Springfield, Illinois (Chapter 8)

- W. H. WARE, The RAND Corporation, Santa Monica, California (Chapters 12 and 13)

- G. P. WEST, Thompson Ramo Wooldridge Inc., Los Angeles, California (Chapter 30)

- J. H. YIENGER, Aeronutronic Systems, Inc., Santa Ana, California (Chapter 5)

#### **FOREWORD**

The proliferation of knowledge now makes it most difficult for scientists or engineers to keep ahead of change even in their own fields, let alone in contiguous fields. One of the fields where recent change has been most noticeable, and in fact exponential, has been automatic control. This three-volume Handbook will aid individuals in almost every branch of technology who must constantly refresh their memories or refurbish their knowledge about many aspects of their work.

Automation, computation, and control, as we know them, have been evolving for centuries, but within the last generation their impact has been felt in nearly every segment of human endeavor. Feedback principles were exploited by Leonardo da Vinci and applied by James Watt. Some of the early theoretical work of importance was contributed by Lord Kelvin, who also, together with Charles Babbage, pointed the way to the development of today's giant computational aids. Since about the turn of the present century, the works of men like Minorsky, Nyquist, Wiener, Bush, Hazen, and von Neumann gave quantum jumps to computation and control. But it was during and immediately following World War II that quantum jumps occurred in abundance. This was the period when theories of control, new concepts of computation, new areas of application, and a host of new devices appeared with great rapidity. Technologists now find these fields charged with challenge, but at the same time hard to encompass. From the activities of World War II such terms as servomechanism, feedback control, digital and analog computer, transducer, and system engineering reached maturity. More recently the word automation has become deeply entrenched as meaning something about the field on which no two people agree.

Philosophically minded technologists do not accept automation merely as a third Industrial Revolution. They see it, as they stand about where the editors of this Handbook stood when they projected this work, as a manifestation of one of the greatest Intellectual Revolutions in Thinking that has occurred for a long time. They see in automation the natural

consequence of man's urge to exploit modern science on a wide front to perform useful tasks in, for example, manufacturing, transportation, business, physical science, social science, medicine, the military, and government. They see that it has brought great change to our conventional way of thinking about the human use of human beings, to quote Norbert Wiener, and in turn about how our engineers will be trained to solve tomorrow's engineering problems. They even see that it has precipitated some deep thinking on the part of our industrial and union leadership about the organization of workers in order not to hold captive bodies of workmen for jobs that automation, computation, and control have swept or will soon sweep away.

Perhaps the important new face on today's technological scene is the degree to which the broad field needs codification and unification in order that technologists can optimize their role to exploit it for the general good. One of the early instances of organized academic instruction in the field was at The Massachusetts Institute of Technology in the Electrical Engineering Department in September 1939, as a course entitled Theory and Application of Servomechanisms. I can well recollect discussions around 1940 with the late Dr. Donald P. Campbell and Dr. Harold L. Hazen, which led temporarily to renaming the course Dynamic Analysis of Automatic Control Systems because so few students knew what "servomechanisms" were. But when the GI's returned from war everybody knew, and everyone wanted instruction. Since that time engineering colleges throughout the land have elected to offer organized instruction in a multitude of topics ranging from the most abstract mathematical fundamentals to the most specific applications of hardware. Textbooks are available on every subject along this broad spectrum. But still the practicing control or computer technologist experiences great difficulty keeping abreast of what he needs to know.

As organized instruction appeared in educational institutions, and as industrial activity increased, professional societies organized groups in the areas of control and computation to meet the needs of their members to tell one another about technical advances. Within the past five years several trade journals have undertaken to report regularly on developments in theory, components, and systems. The net effect of all this is that the technologist is overwhelmed with fragmentary, sometimes contradictory, redundant information that comes at him at random and in many languages. The problem of assessing and codifying even a portion of this avalanche of knowledge is beyond the capabilities of even the most able technologist.

The editors of the *Handbook* have rightly concluded that what each technologist needs for his long-term professional growth is to have a body

of knowledge that is negotiable at par in any one of a number of related fields for many years to come. It would be ideal, of course, if a college education could give a prospective technologist this kind of knowledge. It is in the hope of doing this that engineering curricula are becoming more broadly based in science and engineering science. But it is unlikely that even this kind of college training will be adequate to cope with the consequences of the rapid proliferation of technology as is manifest in the area of automation, computation, and control. Hence, handbooks are an essential component of the technical literature when they provide the unity and continuity that are requisite.

I can think of no better way to describe this *Handbook* than to say that the editors, in both their organization of material and selection of substance, have given technologists a unified work of lasting value. It truly represents today's optimum package of that body of knowledge that will be negotiable at par by technologists for many years to come in a wide range of disciplines.

GORDON S. BROWN

Dean, School of Engineering

Massachusetts Institute of Technology

## **PREFACE**

Accelerated advances in technology have brought a steady stream of automatic machines to our factories, offices, and homes. The earliest automation forms were concerned with doing work, followed by the controlling function, and recently the big surge in automation has been directed toward data handling functions. New devices ranging from digital computers to satellites have resulted from military and other government research and development programs. Such activity will continue to have an important impact on automation progress.

One of the pressures for the development of automation has been the growing complexity and speed of business and industrial operations. But automation in turn accelerates the tempo of whatever it touches, so that we can expect future systems to be even larger, faster, and more complex. While a segment of engineering will continue to mastermind, by rule of thumb procedures, the design and construction of automatic equipment and systems, a growing percentage of engineering effort will be devoted to activities that may be classified as problem solving. The activities of the problem solver involve analysis of previous behavior of systems and equipment, simulation of present situations, and predictions about the future. In the past, problem solving has largely been practiced by engineers and scientists, using slide rules and hand calculators, but with the advent of large-scale data processing systems, the range of applications has been broadened considerably to include economic, government, and social activities. Air traffic control, traffic simulation, library searching, and language translation, are typical of the problems that have been attacked.

This *Handbook* is directed toward the problem solvers—the engineers, scientists, technicians, managers, and others from all walks of life who are concerned with applying technology to the mushrooming developments in automatic equipment and systems. It is our purpose to gather together in one place the available theory and information on general mathematics, feedback control, computers, data processing, and systems

xii PREFACE

design. The emphasis has been on practical methods of applying theory, new techniques and components, and the ever broadening role of the electronic computer. Each chapter starts with definitions and descriptions aimed at providing perspective and moves on to more complicated theory, analysis, and applications. In general, the *Handbook* assumes some engineering training and will serve as an information source and refresher for practicing engineers. For management, it will provide a frame of reference and background material for understanding modern techniques of importance to business and industry. To others engaged in various ramifications of automation systems, the *Handbook* will provide a source of definitions and descriptive material about new areas of technology.

It would be difficult for any one individual or small group of individuals to prepare a handbook of this type. A large number of contributors, each with a field of specialty, is required to provide the engineer with the desired coverage. With such a broad field, it is difficult to treat all material in a homogeneous manner. Topics in new fields are given in more detail than the older, established ones since there is a need for more background information on these new subjects. The organization of the material is in three volumes as shown on the inside cover of the *Handbook*. Volume 1 is on *Control Fundamentals*, Volume 2 is concerned with *Computers and Data Processing*, and Volume 3 with *Systems and Components*.

In keeping with the purpose of this *Handbook*, Volume 1 has a strong treatment of general mathematics which includes chapters on subjects not ordinarily found in engineering handbooks. These include sets and relations, Boolean algebra, probability, and statistics. Additional chapters are devoted to numerical analysis, operations research, and information theory. Finally, the present status of feedback control theory is summarized in eight chapters. Components have been placed with systems in Volume 3 rather than with control theory in Volume 1, although any discussion of feedback control must, of necessity, be concerned with components.

The importance of computing in research, development, production, real time process control, and business applications, has steadily increased. Hence, Volume 2 is devoted entirely to the design and use of analog and digital computers and data processors. In addition to covering the status of knowledge today in these fields, there are chapters on unusual computer systems, magnetic core and transistor circuits, and an advanced treatment of programming. Volume 3 emphasizes systems engineering. A part of the volume covers techniques used in important industrial applications by examining typical systems. The treatment of components

is largely concerned with how to select components among the various alternates, their mathematical description and their integration into systems. There is also a treatment of the design of components of considerable importance today. These include magnetic amplifiers, semiconductors, and gyroscopes.

. We consider this Handbook a pioneering effort in a field that is steadily pushing back frontiers. It is our hope that these volumes will not only provide basic information on new fields, but also will inspire work and further research and development in the fields of automatic control. The editors are pleased to acknowledge the advice and assistance of Dean Gordon S. Brown and Professor Jerome B. Wiesner of the Massachusetts Institute of Technology, and Dr. Brockway McMillan of the Bell Telephone Laboratories, in organizing the subject matter. the contributors goes the major credit for providing clear, thorough treatments of their subjects. The editors are deeply indebted to the large number of specialists in the control field who have aided and encouraged this undertaking by reviewing manuscripts and making valuable suggestions. Many members of the technical staff and secretarial staff of Thompson Ramo Wooldridge Inc. and the Ramo-Wooldridge Division have been especially helpful in speeding the progress of the Handbook.

> EUGENE M. GRABBE SIMON RAMO DEAN E. WOOLDRIDGE

June 1959

**COMPUTER TERMINOLOGY**

Chapter 1.

A.

В.

|         |      | References I-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| DIGITAL | COMP | UTER PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

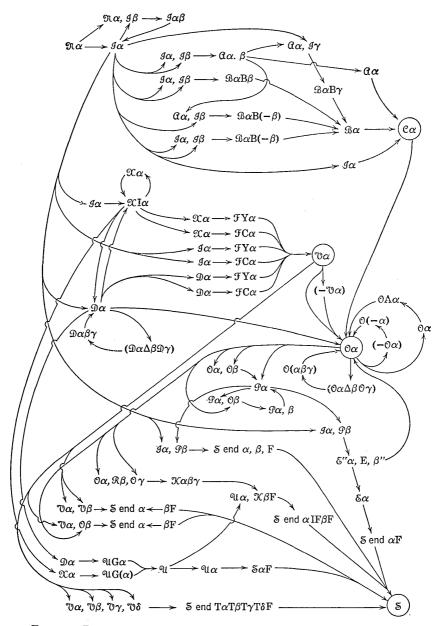

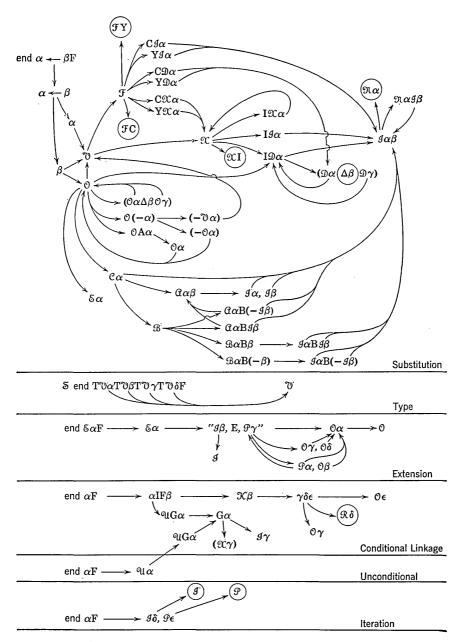

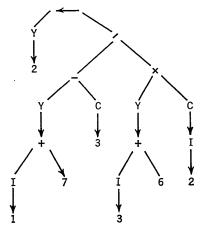

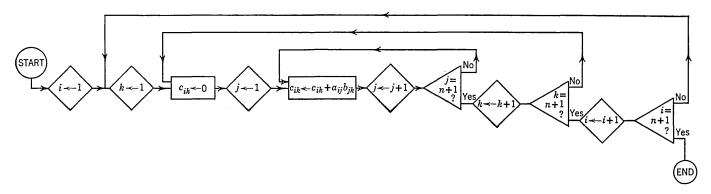

| Chapter | 2.   | 1. Nature of Programming 2-01 2. Numbers and Scale Factors 2-12 3. Number Conversion Tables 2-26 4. Program Structure and Flow Diagrams 2-44 5. Machine Logic 2-53 6. Instruction Logic of Common Computers 2-63 7. Traditional Programming Techniques 2-128 8. Automatic Programming: Development and Objectives 2-155 9. Automatic Programming: Assembly Programs 2-163 10. Automatic Programming: Subroutines, Subroutine Generators, Utility Programs and Integrated Systems 2-167 11. Automatic Programming: Languages, Compilers, and Translators 2-186 | 2-01 |

|         |      | xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

**Computer Terminology and Symbols**

3. Glossary of Terminology 1-02

1. Standardization 1-01

2. Symbols I-01

1-01

Languages 2-244

16. Logical Programming 2-246

17. Microprogramming 2-251

Automatic Programming: The IT Translator; Translator Construction 2-200

Automatic Programming: A Soviet Algebraic Language Compiler 2-228

Automatic Programming: Interpreters

15. Automatic Programming: Recursive

|    |               | <ol> <li>Programs for Maintenance of Equipment 2-258</li> </ol>                                                                                                                                                                                                                                                                  |

|----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |               | <ol> <li>Programming with Natural Language</li> <li>2-259</li> </ol>                                                                                                                                                                                                                                                             |

|    |               | Literature, Acknowledgments, and References 2-260                                                                                                                                                                                                                                                                                |

| c. | THE USE OF DI | GITAL COMPUTERS AND DATA PROCESSORS                                                                                                                                                                                                                                                                                              |

|    | Chapter 3.    | <ol> <li>Data Processing Operations</li> <li>Introduction 3-01</li> <li>Data Collection 3-02</li> <li>Data Conversion, Transcription, and Editing 3-03</li> <li>Data Output 3-04</li> <li>On-Line Versus Off-Line Processing 3-04</li> <li>Scientific Data Manipulation 3-05</li> <li>Business Data Manipulation 3-06</li> </ol> |

|    | Chapter 4.    | 8. Checking 3-13  Quantitative Characteristics of Data  Processing Systems 4-01                                                                                                                                                                                                                                                  |

|    |               | <ol> <li>Determining System Requirements 4-01</li> <li>Basic System Characteristics 4-02</li> <li>Basic Equipment Characteristics 4-04</li> <li>Measurement of System Factors 4-04</li> <li>Relating System Characteristics to Equipment Characteristics 4-09 References 4-16</li> </ol>                                         |

|         |     | CONTENTS                                                                                                                                                                                                                                                                                                                         | xvii |

|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

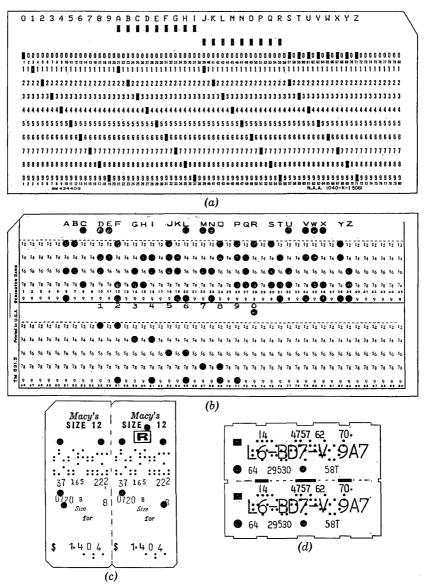

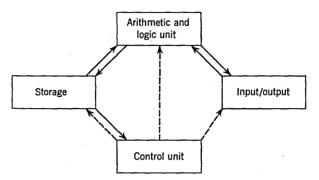

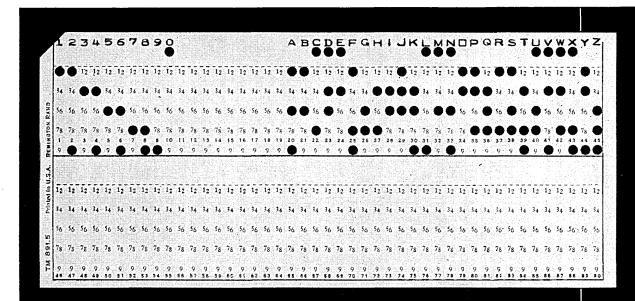

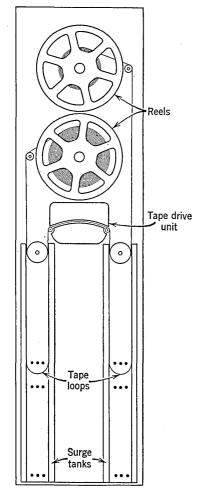

| Chapter | 5.  | Equipment Description  1. General Equipment Description 5-01 2. Characteristics of Electronic Data Processing Equipment 5-04 3. Input Equipment 5-09 4. Storage Equipment 5-24 5. Output Equipment 5-33 6. Arithmetic and Logic Unit 5-38 7. Control Equipment 5-40 8. Typical Electronic Digital Equipment 5-43 References 5-43 | 5-01 |

| Chapter | 6.  | Facility Requirements  1. Physical Installation 6-01  2. Personal Requirements 6-09 References 6-13                                                                                                                                                                                                                              | 6-01 |

| Chapter | 7.  | Design of Business Systems  1. General System Requirements 7-01 2. Stages of System Evolution 7-02 3. Detailed Steps of System Design 7-03 4. Economic Impacts of System Changes 7-12 References 7-14                                                                                                                            | 7-01 |

| Chapter | 8.  | Accounting Applications  1. Life Insurance 8-01 2. Casualty Insurance 8-08 3. Public Utility Customer Billing 8-11 4. Payroll 8-15                                                                                                                                                                                               | 8-01 |

| Chapter | 9.  | Inventory and Scheduling Applica-<br>tions                                                                                                                                                                                                                                                                                       | 9-01 |

| Chapter | 10. | Scientific and Engineering Applica-                                                                                                                                                                                                                                                                                              |      |

1. Introduction 10-01

2. Simultaneous Linear Algebraic Equations and Matrix Inversion 10-02

10-01

|    |               | <ul> <li>3. Characteristic Roots and Vectors 10-04</li> <li>4. Linear Programming 10-06</li> <li>5. Differential Equations 10-08</li> <li>6. Statistical Analysis 10-10 References 10-12</li> </ul>                                                                                                                                                   |       |

|----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | Chapter 11.   | Handling of Non-Numerical Information  1. Introduction 11-01 2. Performing Logic on a Digital Computer 11-02 3. Game Playing Machines 11-11 4. The Machine Translation of Languages 11-13 5. Automatic Literature Searching and Retrieval 11-16 References 11-19                                                                                      | 11-01 |

| D. | DESIGN OF DIG | GITAL COMPUTERS                                                                                                                                                                                                                                                                                                                                       |       |

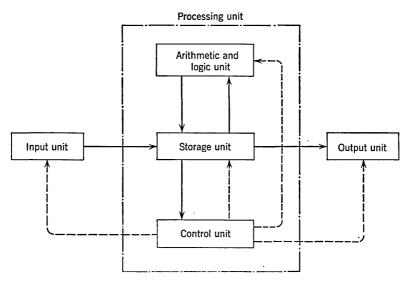

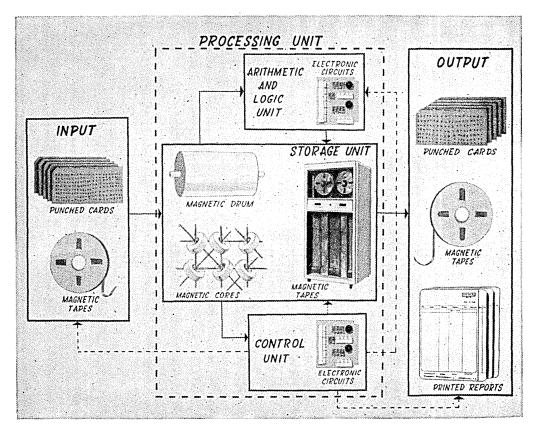

|    | Chapter 12.   | <ol> <li>Digital Computer Fundamentals</li> <li>Digital Computers and Control Systems 12-01</li> <li>Digital Computer Fundamentals 12-02</li> <li>Machine Construction 12-07</li> <li>Number Systems and Number Codes 12-12</li> <li>Machine Number Systems 12-18</li> <li>Computer Design Characteristics 12-25</li> <li>References 12-30</li> </ol> | 12-01 |

|    | Chapter 13.   | <ol> <li>Techniques for Reliability</li> <li>Introduction 13-01</li> <li>Summary of Operating and Design Techniques 13-02</li> <li>Operating Techniques 13-04</li> <li>System Design 13-05</li> <li>Circuit Design 13-07</li> <li>Maintenance 13-08         References 13-10     </li> </ol>                                                          | 13-01 |

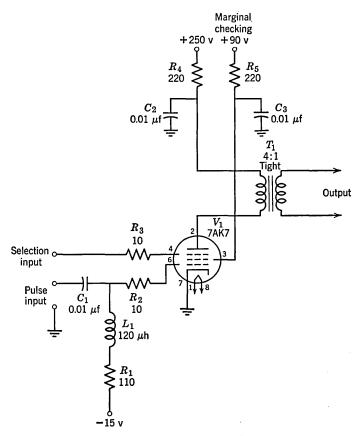

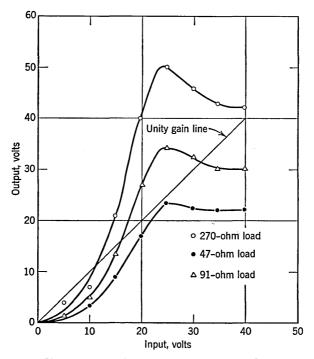

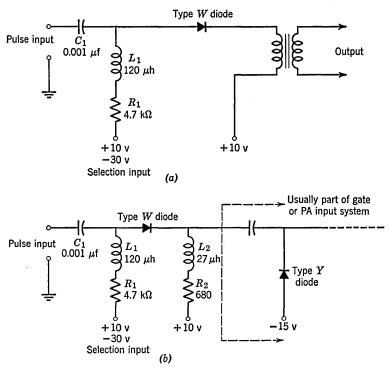

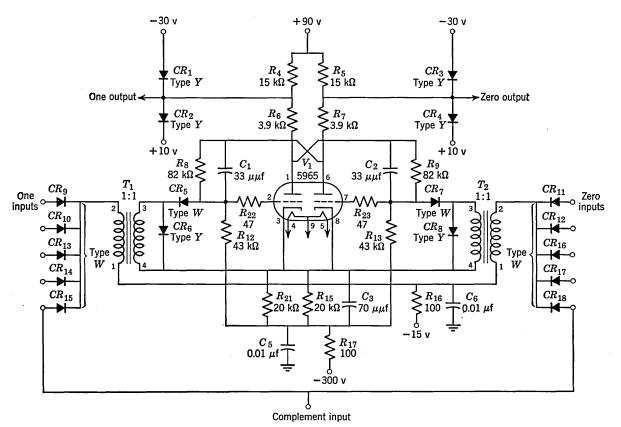

| Chapter | 14. Co  | mponents and Basic Circuits .                                             | 14-01 |

|---------|---------|---------------------------------------------------------------------------|-------|

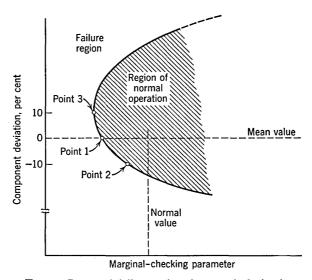

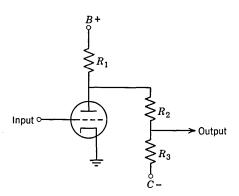

|         | 1.      | Designing for Reliability 14-01                                           |       |

|         | 2.      | Components and Circuit Design 14-03                                       |       |

|         | 3.      | Marginal Checking 14-05                                                   |       |

|         |         | Reliable Computer Circuits 14-19                                          |       |

|         |         | Components, Characteristics, and Ap-                                      |       |

|         |         | plication Notes 14-43                                                     |       |

|         | 6.      | Transistors 14-51                                                         |       |

|         |         | References 14-54                                                          |       |

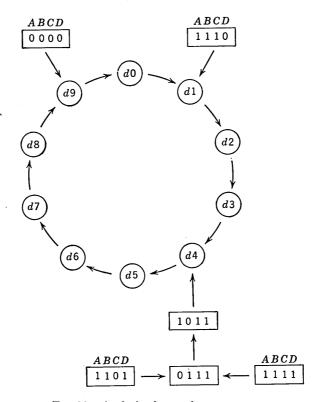

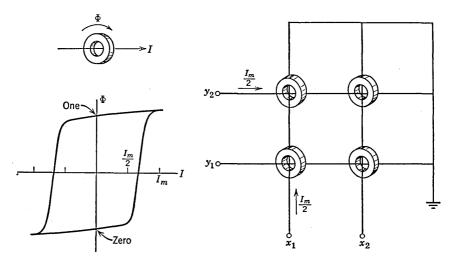

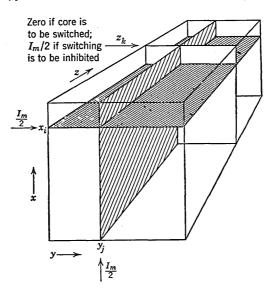

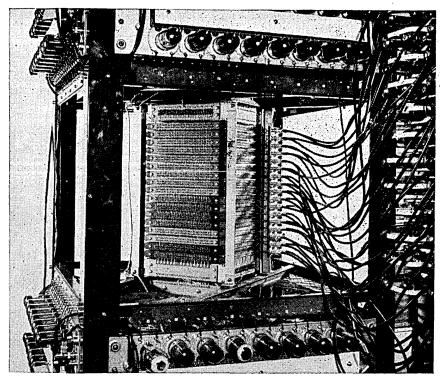

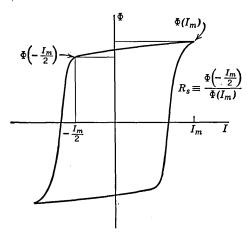

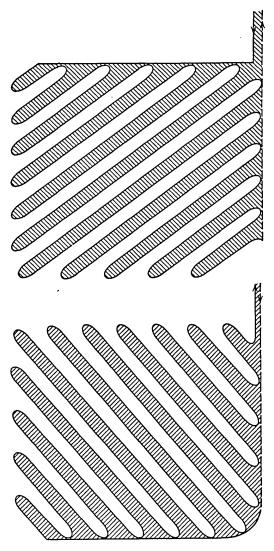

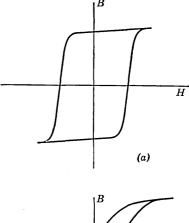

| Chapter | 15. Ma  | ignetic Core Circuits                                                     | 15-01 |

|         |         | Fundamentals 15-01                                                        |       |

|         |         | Magnetic Cores 15-04                                                      |       |

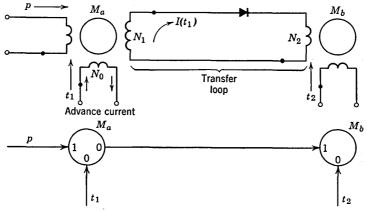

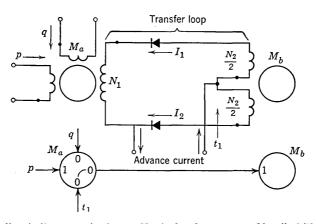

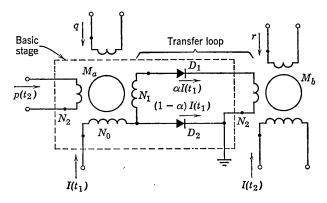

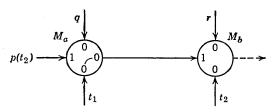

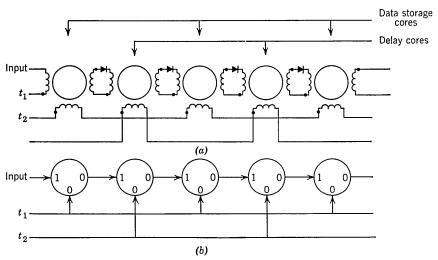

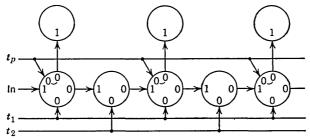

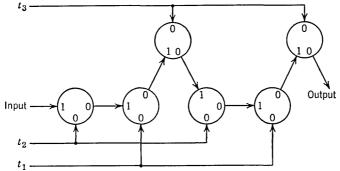

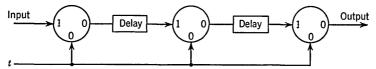

|         |         | Transfer Loops 15-09                                                      |       |

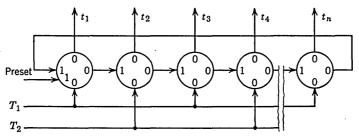

|         |         | Magnetic Shift Registers 15-15                                            |       |

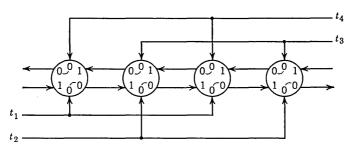

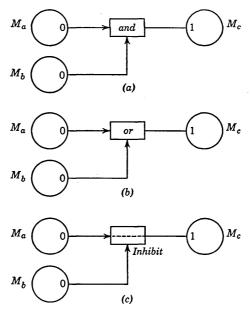

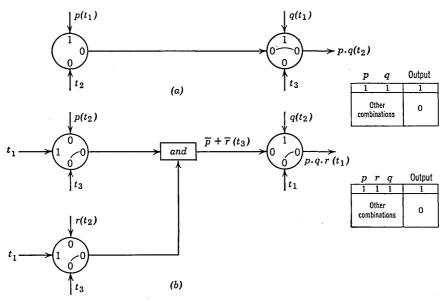

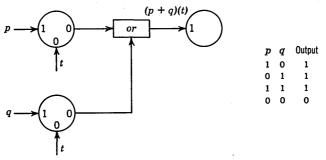

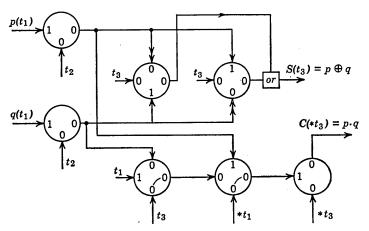

|         |         | Logical Function Elements 15-16                                           |       |

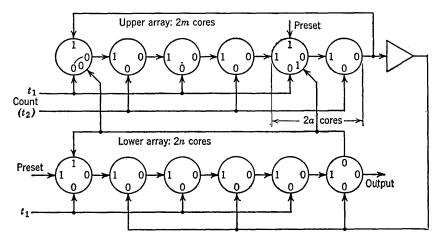

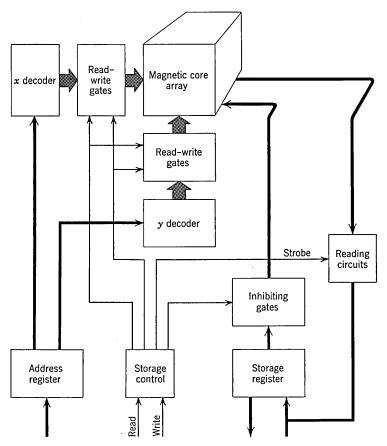

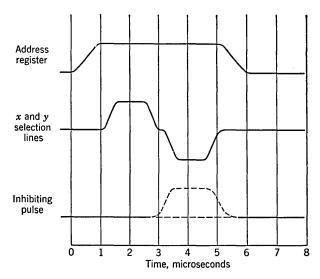

|         |         | Magnetic Core Storages 15-19                                              |       |

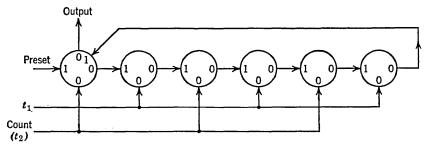

|         |         | Timing Control Circuits 15-21                                             |       |

|         | 8.      | Arithmetic and Miscellaneous Appli-                                       |       |

|         | 0       | cations 15-22  Drivers for Magnetic Core Circuits                         |       |

|         | 7.      | 15-23                                                                     |       |

|         |         | References 15-24                                                          |       |

| Chamton | 1.6 Tue | ınsistor Circuits                                                         | 16-01 |

| Chapter |         |                                                                           | 10-01 |

|         |         | Introduction 16-01                                                        |       |

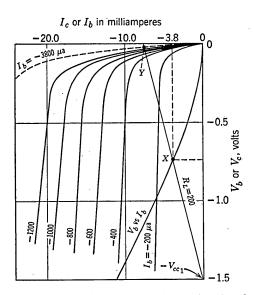

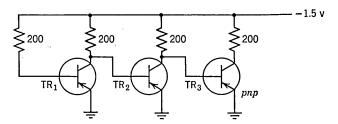

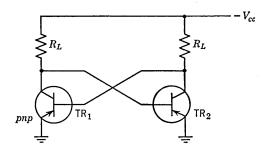

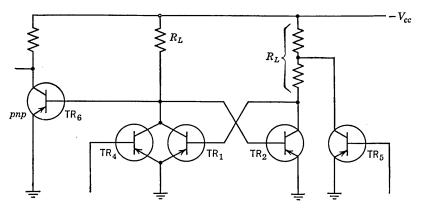

|         |         | Transistor Switching Properties 16-02 Direct-Coupled Transistor Switching |       |

|         | ٥.      | Circuits 16-05                                                            |       |

|         | . 4     | Point-Contact Transistor Pulse Ampli-                                     |       |

|         | ••      | fiers 16-15                                                               |       |

|         | 5.      | Transistorized Calculator 16-20                                           |       |

|         |         | References 16-30                                                          |       |

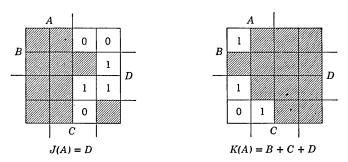

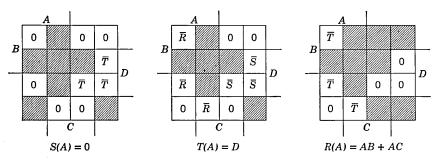

| Chapter | 17. Log | gical Design                                                              | 17-01 |

|         | Ι.      | Computer Elements 17-01                                                   |       |

|         | 2.      | Algebraic Techniques of Logical De-                                       |       |

|         |         | sign 17-10                                                                |       |

|         | 3.      | Preliminary Design Considerations 17-24                                   |       |

|         | 4       | Detailed Logical Design 17-30                                             |       |

|         |         |                                                                           |       |

5. Direct Simulation of a Logical Design

|    |             | 17-38<br>References 17-42                                                                                                                                                                                                                                                          |

|----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Chapter 18. | Arithmetic and Control Elements  1. System Considerations 18-01  2. Notation 18-02  3. Binary Operations 18-03  4. Decimal Operations 18-25  5. Special Operations 18-30  6. Control Elements 18-33  References 18-40                                                              |

|    | Chapter 19. | Storage                                                                                                                                                                                                                                                                            |

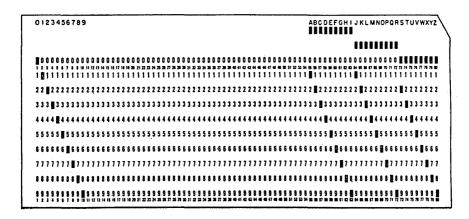

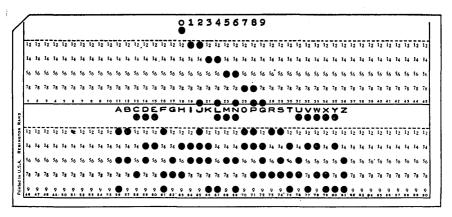

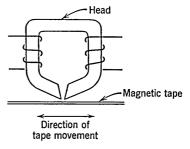

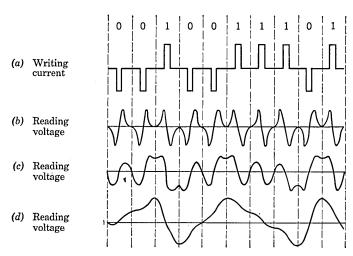

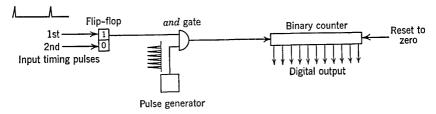

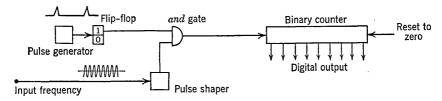

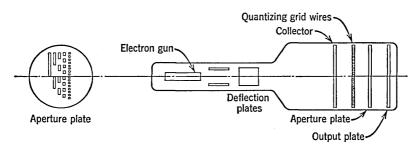

|    | Chapter 20. | Input-Output Equipment for Digital Computers 20-01  1. The Input-Output System 20-01 2. Printed Page 20-06 3. Perforated Tape 20-19 4. Punched Card Machines 20-30 5. Magnetic Tape 20-33 6. Analog-Digital Conversion 20-44 References 20-66                                      |

| E. | DESIGN AND  | APPLICATION OF ANALOG COMPUTERS                                                                                                                                                                                                                                                    |

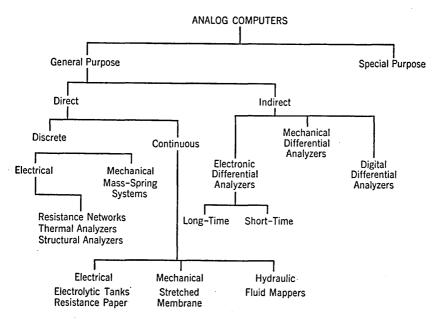

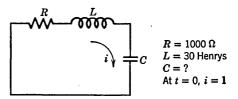

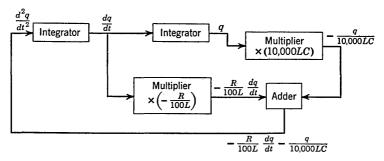

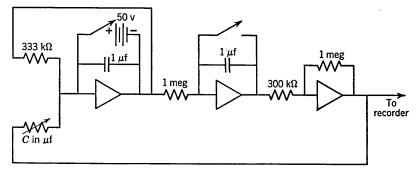

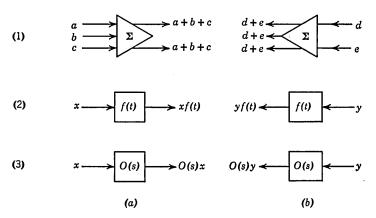

|    | Chapter 21. | <ol> <li>Analog Computation in Engineering 21-01</li> <li>Definition of Analog Computation 21-01</li> <li>Classification of Analog Computers 21-02</li> <li>Requirements of Analog Computers 21-05</li> <li>General Steps in the Solution of Engineering Problems 21-06</li> </ol> |

|            | 5.                               | Areas of Application of Analog Computers 21-09                                                                                                                                                                                                                                                                                                                                                                     |       |

|------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

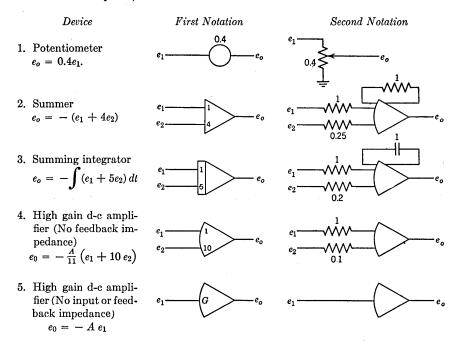

|            | . 6.                             | . Symbols and Diagram Notation 21-11                                                                                                                                                                                                                                                                                                                                                                               |       |

|            |                                  | References 21-11                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Chapter    |                                  | near Electronic Computer Elements                                                                                                                                                                                                                                                                                                                                                                                  | 22-01 |

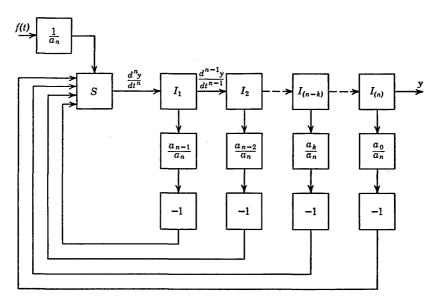

|            | 1.                               | Introduction and Computer Diagram  Notation 22-01                                                                                                                                                                                                                                                                                                                                                                  |       |

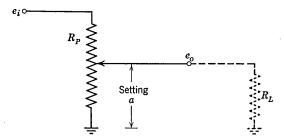

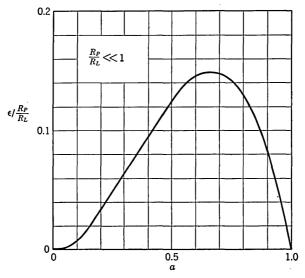

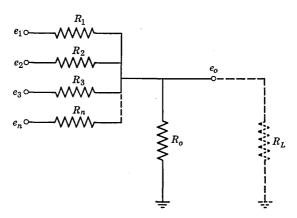

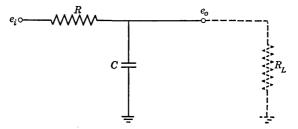

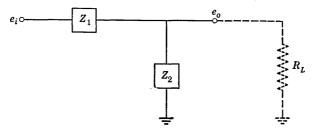

|            | 2.                               | . Passive Computer Elements 22-04                                                                                                                                                                                                                                                                                                                                                                                  |       |

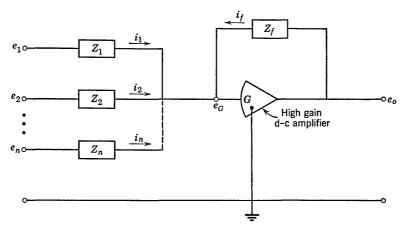

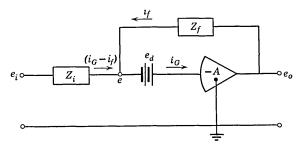

|            |                                  | Direct-Current Operational Amplifiers with Feedback 22-08                                                                                                                                                                                                                                                                                                                                                          |       |

|            | 4.                               | . Scale Factors 22-10                                                                                                                                                                                                                                                                                                                                                                                              |       |

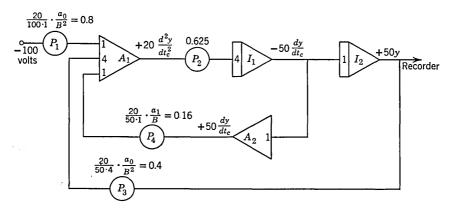

|            | 5.                               | . Typical Problem Setup 22-12                                                                                                                                                                                                                                                                                                                                                                                      |       |

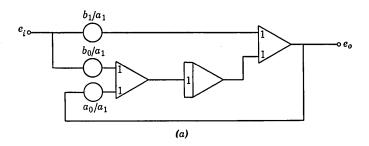

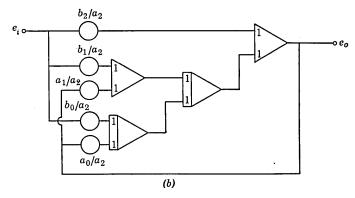

|            | 6.                               | Representation of Complex Transfer Functions 22-13                                                                                                                                                                                                                                                                                                                                                                 |       |

|            | 7.                               | Operational Amplifier Design 22-16                                                                                                                                                                                                                                                                                                                                                                                 |       |

|            | 8.                               | Errors in Linear Computer Elements                                                                                                                                                                                                                                                                                                                                                                                 |       |

|            |                                  | 22-33                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|            |                                  | References 22-37                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Chapter    | 23. No                           | onlinear Electronic Computer Ele-                                                                                                                                                                                                                                                                                                                                                                                  |       |

| onapio.    | 20                               | manage and the competer and                                                                                                                                                                                                                                                                                                                                                                                        |       |

| diapioi    |                                  | ents                                                                                                                                                                                                                                                                                                                                                                                                               | 23-01 |

| Chapto.    | me                               |                                                                                                                                                                                                                                                                                                                                                                                                                    | 23-01 |

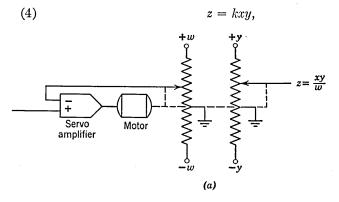

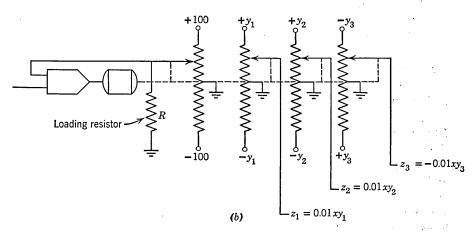

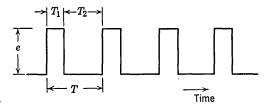

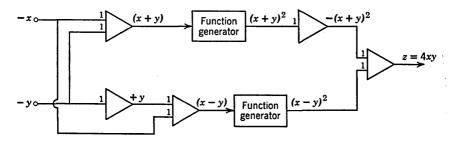

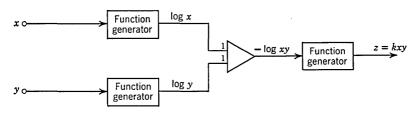

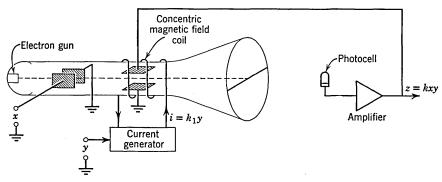

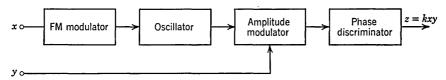

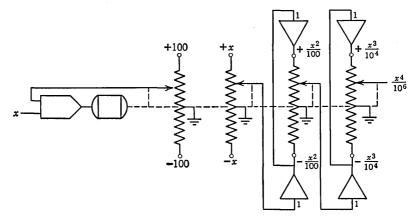

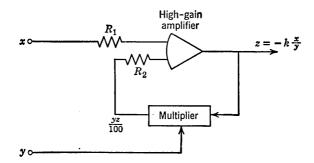

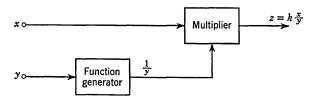

| - Citapioi | me<br>                           | e <b>nts</b><br>. Function Multipliers 23-01<br>. Function Generators 23-14                                                                                                                                                                                                                                                                                                                                        | 23-01 |

| - Chapter  | 1.<br>2.<br>3.                   | ents  Function Multipliers 23-01  Function Generators 23-14  Switching Devices 23-22                                                                                                                                                                                                                                                                                                                               | 23-01 |

| ·          | me<br>1.<br>2.<br>3.<br>4.       | ents  Function Multipliers 23-01  Function Generators 23-14  Switching Devices 23-22  Trigonometric Devices 23-31                                                                                                                                                                                                                                                                                                  | 23-01 |

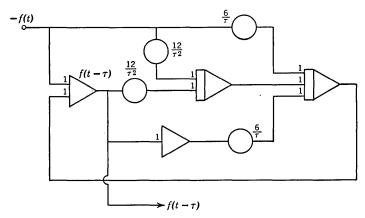

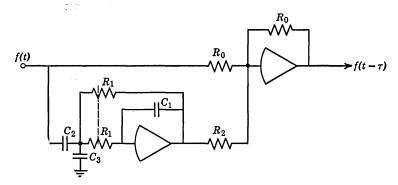

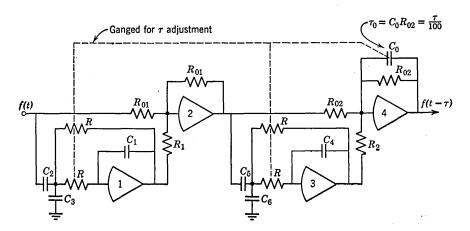

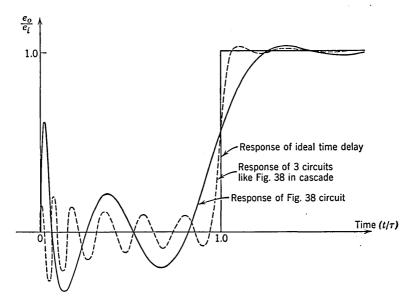

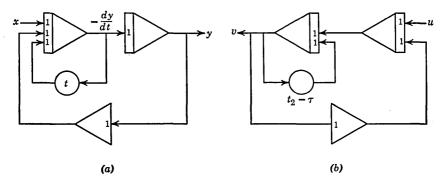

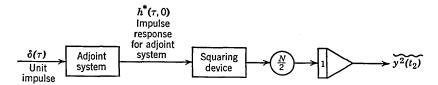

| ·          | me<br>1.<br>2.<br>3.<br>4.       | ents  Function Multipliers 23-01  Function Generators 23-14  Switching Devices 23-22  Trigonometric Devices 23-31  Time Delay Simulators 23-34                                                                                                                                                                                                                                                                     | 23-01 |

| ·          | me<br>1.<br>2.<br>3.<br>4.       | ents  Function Multipliers 23-01  Function Generators 23-14  Switching Devices 23-22  Trigonometric Devices 23-31                                                                                                                                                                                                                                                                                                  | 23-01 |

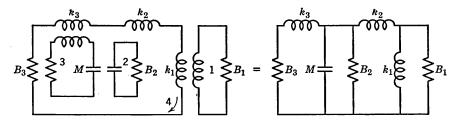

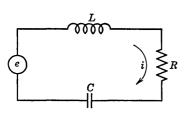

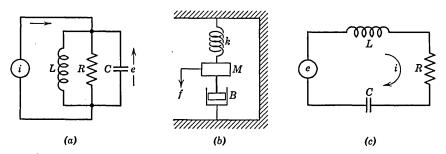

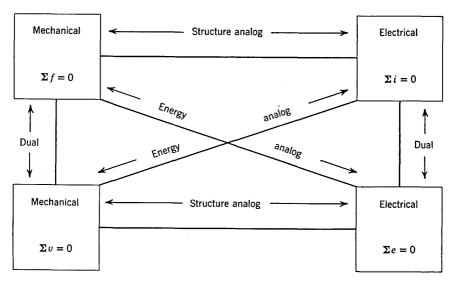

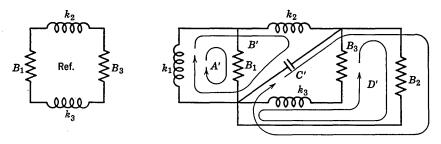

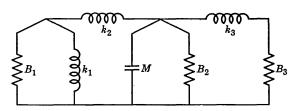

| Chapter    | me<br>1.<br>2.<br>3.<br>4.<br>5. | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Tallogs and Duals of Physical Sys-                                                                                                                                                                                                                    |       |

|            | 1.<br>2.<br>3.<br>4.<br>5.       | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Talogs and Duals of Physical Sysmus                                                                                                                                                                                                                   | 23-01 |

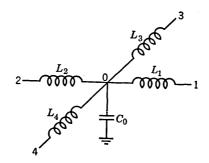

|            | 24. An ter                       | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Ralogs and Duals of Physical Sysms Electric Analogy of Dynamic System 24-01                                                                                                                                                                           |       |

|            | 24. An ter 1.                    | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Halogs and Duals of Physical Sysms Electric Analogy of Dynamic System 24-01 General Terminology 24-03                                                                                                                                                 |       |

|            | 24. An ter 1.                    | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Malogs and Duals of Physical Sysmus Electric Analogy of Dynamic System 24-01 General Terminology 24-03 Analysis of General Systems 24-03                                                                                                              |       |

|            | 24. Antel                        | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Italogs and Duals of Physical Sysmus Electric Analogy of Dynamic System 24-01 General Terminology 24-03 Analysis of General Systems 24-03 Energy Considerations 24-07                                                                                 |       |

|            | 24. An ter 1. 2. 3. 4. 5.        | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Malogs and Duals of Physical Sysmus Electric Analogy of Dynamic System 24-01 General Terminology 24-03 Analysis of General Systems 24-03 Energy Considerations 24-07 Duality 24-08                                                                    |       |

|            | 24. An ter 1. 2. 3. 4. 5. 6.     | Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Malogs and Duals of Physical Sysmus Electric Analogy of Dynamic System 24-01 General Terminology 24-03 Analysis of General Systems 24-03 Energy Considerations 24-07 Duality 24-08 Construction of Duals 24-09                                              |       |

|            | 24. An ter 1. 2. 3. 4. 5. 6.     | Ents  Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Malogs and Duals of Physical Sysmas Electric Analogy of Dynamic System 24-01 General Terminology 24-03 Analysis of General Systems 24-03 Energy Considerations 24-07 Duality 24-08 Construction of Duals 24-09 Across and Through Variables in Physi- |       |

|            | 24. An ter 1. 2. 3. 4. 5. 6.     | Function Multipliers 23-01 Function Generators 23-14 Switching Devices 23-22 Trigonometric Devices 23-31 Time Delay Simulators 23-34 References 23-39  Malogs and Duals of Physical Sysmus Electric Analogy of Dynamic System 24-01 General Terminology 24-03 Analysis of General Systems 24-03 Energy Considerations 24-07 Duality 24-08 Construction of Duals 24-09                                              |       |

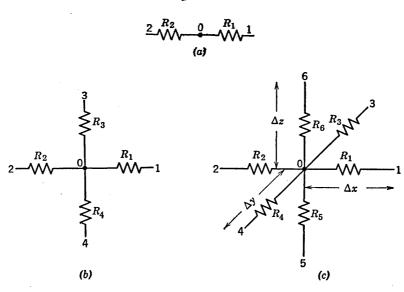

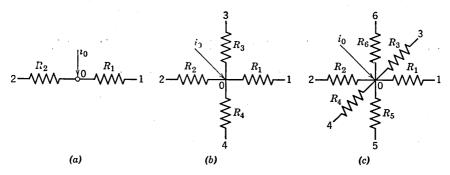

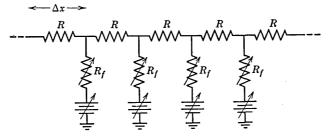

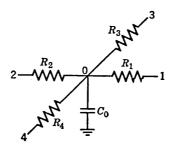

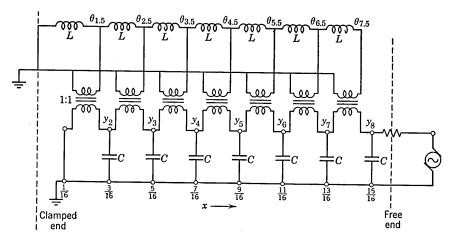

| Chapter 25. | Solution of Field Problems                                                                                                                                                                                                                                                                                                                                                                                                                      | 25-01 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|             | <ol> <li>Formulation of Engineering Problems<br/>as Partial Differential Equations<br/>25-01</li> </ol>                                                                                                                                                                                                                                                                                                                                         |       |

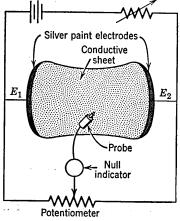

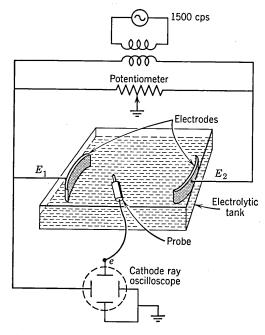

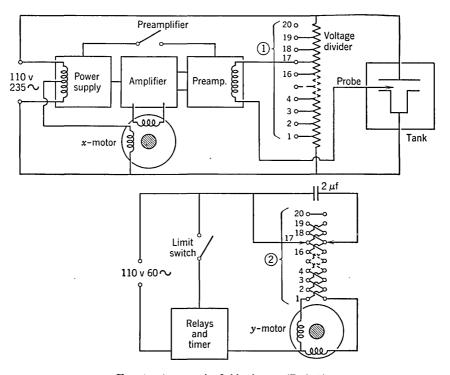

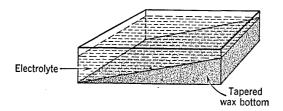

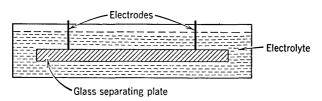

|             | 2. Continuous Type Electric Analogs<br>25-05                                                                                                                                                                                                                                                                                                                                                                                                    |       |

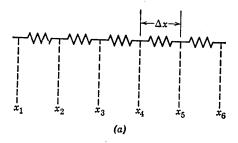

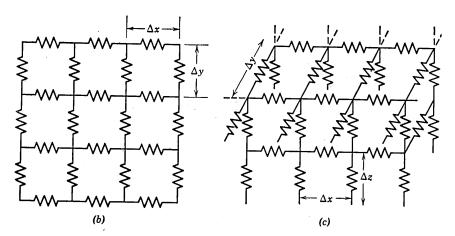

|             | 3. Discrete Element Type Electric Analogs 25-11                                                                                                                                                                                                                                                                                                                                                                                                 |       |

|             | 4. Nonelectric Field Analogs 25-22<br>References 25-23                                                                                                                                                                                                                                                                                                                                                                                          |       |

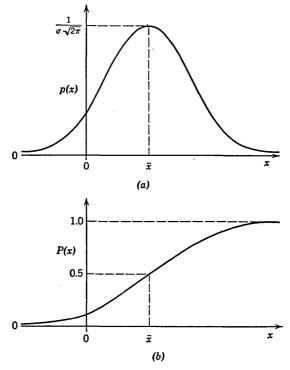

| Chapter 26. | Noise and Statistical Techniques                                                                                                                                                                                                                                                                                                                                                                                                                | 26-01 |

|             | 1. Introduction and Definition 26-01                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|             | 2. Random Variable Concepts 26-02                                                                                                                                                                                                                                                                                                                                                                                                               |       |

|             | 3. Treatment of Linear Systems 26-06                                                                                                                                                                                                                                                                                                                                                                                                            |       |

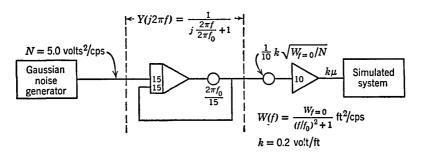

|             | 4. Treatment of Nonlinear Systems 26-09                                                                                                                                                                                                                                                                                                                                                                                                         |       |

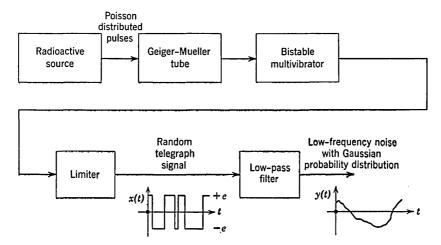

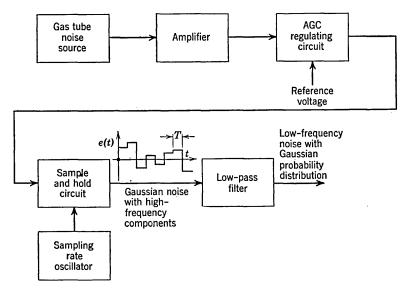

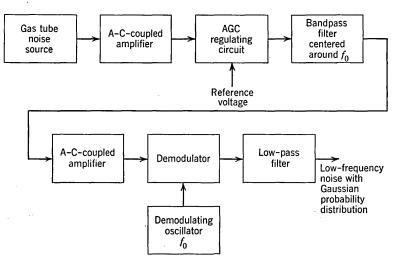

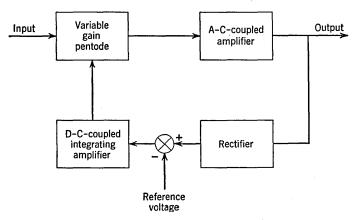

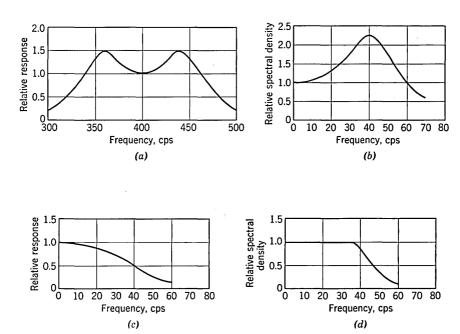

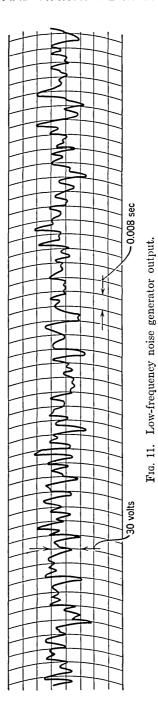

|             | 5. Noise Generators 26-12                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|             | References 26-20                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

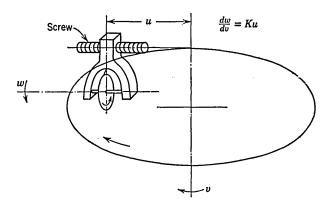

| Chapter 27. | Mechanical Computer Elements .                                                                                                                                                                                                                                                                                                                                                                                                                  | 27-01 |

| Chapter 27. | Mechanical Computer Elements .  1. Introduction 27-01                                                                                                                                                                                                                                                                                                                                                                                           | 27-01 |

| Chapter 27. | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27-01 |

| Chapter 27. | 1. Introduction 27-01                                                                                                                                                                                                                                                                                                                                                                                                                           | 27-01 |

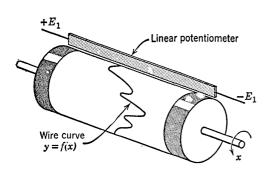

| Chapter 27. | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> </ol>                                                                                                                                                                                                                                                                                                  | 27-01 |

| Chapter 27. | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14</li> </ol>                                                                                                                                                                                                                                                                     | 27-01 |

| Chapter 27. | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> </ol>                                                                                                                                                                                                                                                                                                  | 27-01 |

| Chapter 27. | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> </ol>                                                                                                                                                                                                                                       | 27-01 |

|             | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> </ol>                                                                                                                                                                                                                                       | 22.21 |

|             | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> <li>Digital Techniques in Analog Computation         Introduction 28-01     </li> </ol>                                                                                                                                                     | 22.21 |

|             | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> <li>Digital Techniques in Analog Computation         <ol> <li>Introduction 28-01</li> <li>Digital Differential Analyzer 28-02</li> </ol> </li> </ol>                                                                                        | 22.21 |

|             | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> <li>Digital Techniques in Analog Computation         Introduction 28-01     </li> </ol>                                                                                                                                                     | 22.21 |

|             | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> <li>Digital Techniques in Analog Computation         <ol> <li>Introduction 28-01</li> <li>Digital Differential Analyzer 28-02</li> <li>Digital Operational Computers 28-11</li> <li>Auxiliary Digital Computer Tech-</li> </ol> </li> </ol> | 22.21 |

|             | <ol> <li>Introduction 27-01</li> <li>Basic Operations 27-02</li> <li>Function Generation 27-05</li> <li>Solution of Equations 27-09</li> <li>Scale Factors 27-14         References 27-15     </li> <li>Digital Techniques in Analog Computation         <ol> <li>Introduction 28-01</li> <li>Digital Differential Analyzer 28-02</li> <li>Digital Operational Computers 28-11</li> </ol> </li> </ol>                                           | 22.21 |

| UNUSUAL COM | APUTER SYSTEMS                                                                                                                                                                            |       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

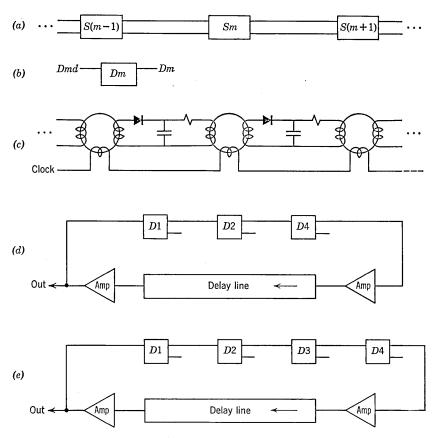

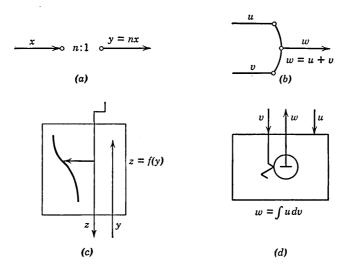

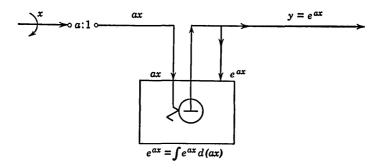

| Chapter 29. | Operational Digital Techniques 1. Introduction 29-01 2. Basic Devices 29-05 3. Applications of Operational Digital Techniques 29-14 4. Incremental Computation 29-17 References 29-29     | 29-01 |

| Chapter 30. | Combined Analog-Digital Computer                                                                                                                                                          |       |

|             | Systems                                                                                                                                                                                   | 30-01 |

|             | <ol> <li>Description and Applications 30-01</li> <li>System Components 30-02</li> <li>Control and Timing 30-08</li> <li>Modes of Operation 30-13         References 30-15     </li> </ol> |       |

| Chapter 31. | Simple Turing Type Computers .                                                                                                                                                            | 31-01 |

|             | 1. Basic Concepts 31-01                                                                                                                                                                   |       |

|             | 2. Functional Requirements 31-02                                                                                                                                                          |       |

|             | <ol> <li>Machine Description 31-03</li> <li>Mechanization 31-07</li> </ol>                                                                                                                |       |

|             | 5. Programming 31-09                                                                                                                                                                      |       |

|             | 6. Communication with No Auxiliary                                                                                                                                                        |       |

|             | Storage 31-13                                                                                                                                                                             |       |

|             | 7. Machine Comparison 31-15                                                                                                                                                               |       |

|             | References 31-16                                                                                                                                                                          |       |

**INDEX**

F.

# COMPUTER TERMINOLOGY

#### A. COMPUTER TERMINOLOGY

1. Computer Terminology and Symbols, by E. M. Grabbe

# Computer Terminology and Symbols

E. M. Grabbe

| 1. Standardization         | 1-01 |

|----------------------------|------|

| 2. Symbols                 | I-01 |

| 3. Glossary of Terminology | 1-02 |

| References                 | 1-22 |

#### I. STANDARDIZATION

The growth of analog and digital computers as major components of modern computing and control systems has done much to encourage standardization of terminology and symbols. A sizable part of this effort has been directed toward the terminology of digital computers. Hence, the glossary of terminology given in Sect. 3 is largely concerned with digital terms. No attempt has been made to define the terms associated with computer usage in scientific computation, business data processing, and control applications.

#### 2. SYMBOLS

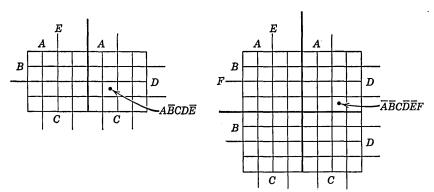

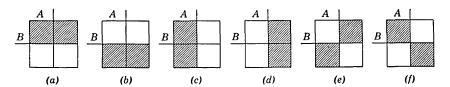

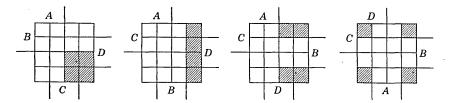

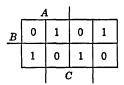

**Diagram Symbols.** Several sets of symbols for schematic and circuit diagrams have been in use in the analog and digital fields. In Part E on analog computers, one set of symbols has been chosen and used throughout the chapters. The alternate notation is also listed for linear computing elements in Chap. 22 (see Table 1).

In the digital field, while terminology has been standardized to some degree, the use of symbols has not. A variety of symbols is employed

for programming, logic, and circuit diagrams, depending on the author's preference and the type of diagram. Some symbols are easier to use for some purposes than others. In all cases the symbols are clearly defined and usage is unambiguous.

Since symbols are not standardized, no detailed list is given, but they are described in the various chapters. The following is a list of the chapters in the Handbook where tables of symbols may be found:

| $\operatorname{Symbols}$       | Chapters                   |

|--------------------------------|----------------------------|

| Digital computer               |                            |

| Programming                    | Chap. 2, Sect. 4           |

| Logical design                 | Chap. 17, Sect. 4          |

| Logical operations             | Chap. 17, Sect. 1, Table 1 |

| Magnetic cores                 | Chap. 15, Sect. 1          |

| Analog computer                | - ,                        |

| Linear computing elements      | Chap. 22, Sect. 1          |

| Nonlinear computing elements   | Chap. 23, Sect. 1          |

| Mechanical computing elements  | Chap. 27, Sect. 2          |

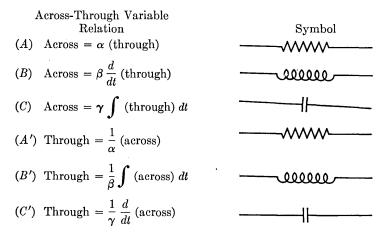

| Analogs and duals              | Chap. 24, Sect. 2          |

| Digital differential analyzers | Chap. 28, Sect. 2          |

Letter Symbols. Letter symbols are standardized to some extent in Part E, Design and Application of Analog Computers. (See Chap. 21, Sect. 1.) Elsewhere letter symbols are defined when they are used.

#### 3. GLOSSARY OF TERMINOLOGY

Terminology from the Institute of Radio Engineers (Ref. 1) and the Association for Computing Machinery (Ref. 2) has been compiled in a glossary. The I.R.E. terminology is largely concerned with digital computer design, although some analog terms are included. The A.C.M. terminology is concerned with programming. Where an overlap exists, the I.R.E. terminology has been selected since it represents the later effort. For some terms, minor changes or additions have been made for clarity and explanatory notes and examples have been added. Some terms are included which have no official definition, and reference to the chapters where they are described and defined is given. For terms not listed in this glossary, please refer to the index.

Terminology is reproduced with the permission of the Institute of Radio Engineers and the Association for Computing Machinery.

#### Glossary of Terminology

Access Time. A time interval which is characteristic of a storage unit, and is essentially a measure of the time required to communicate with that unit. Many definitions of the beginning and ending of this interval are in common use.

**Accumulator.** A device which stores a number and which, on receipt of another number, adds it to the number already stored and stores the sum. *Note*. The term is also applied to devices which function as described but which have other facilities also.

Accuracy. The quality of freedom from mistake or error, that is, of conformity to truth or to a rule. Accuracy is distinguished from precision. Example. A six-place table is more precise than a four-place table. However, if there are errors in the six-place table, it may be either more or less accurate than the four-place table.

**Adder.** A device which can form the sum of two or more numbers or quantities.

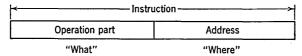

**Address.** An expression, usually numerical, which designates a particular location in a storage or a memory device or other source or destination of information. See also *Instruction Code*.

Absolute address, an address assigned by the machine designer to a particular storage location.

Relative address, the address used to identify a word in a routine or subroutine with respect to its position in that routine or subroutine.

**Symbolic address** (floating address), an address chosen to identify a particular word, function, or other information in a routine, independent of the location of the information within the routine. Sometimes called *symbol* or *tag*.

**Address Part.** In an instruction, any part that is usually an address. See also *Instruction Code*.

**Analog** (in electronic computers). A physical system on which the performance of measurements yields information concerning a class of mathematical problems.

Analog Computer. A physical system together with means of control for the performance of measurements (upon the system) which yield information concerning a class of mathematical problems.

And Circuit. Synonym for and gate.

**And Gate.** A gate whose output is energized when and only when every input is in its prescribed state. Thus, this gate performs the function of the logical and.

Arithmetic Element. Synonym for arithmetic unit.

**Arithmetic Unit.** That part of a computer which performs arithmetic and logical operations.

Assemble; Assembler, Assembly Routine; Assembly. See Routine. Automatic Check. See Check, Automatic.

Band. A group of tracks on a magnetic drum.

Base. See Positional Notation.

Binary. See Positional Notation.

Binary Cell. An elementary unit of storage which can be placed in either of two stable states.

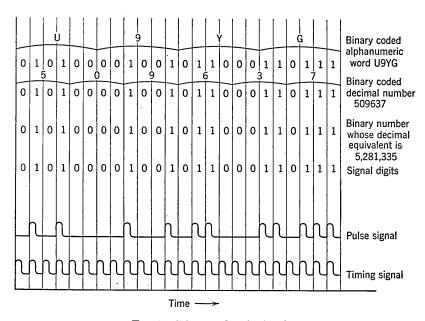

**Binary-Coded-Decimal System.** A system of number representation in which each decimal digit is represented by a group of binary digits. *Note.* Usually refers to the four position binary codes 0000 to 1001 (decimal 1 to 9). Another example is the excess-three code.

Binary Number System. See Positional Notation.

Binary Point. See Point.

Biquinary. See Positional Notation.

**Bit.** (1) An abbreviation of "binary digit." (2) A single character of a language employing exactly two distinct kinds of characters. (3) A unit of information capacity of a storage device. The capacity in bits is the logarithm to the base two of the number of possible states of the device. See also *Storage Capacity*.

Block. A group of words considered as a unit.

Borrow. See Carry.

**Branch.** A synonym for conditional jump.

**Break Point.** A point in a routine at which a special instruction is inserted which, if desired, will cause a digital computer to stop for a visual check of progress.

**Buffer.** (1) An isolating circuit used to avoid reaction of a driven circuit on the corresponding driving circuit. (2) A storage device used to compensate for a difference in rate of flow of information or time of occurrence of events when transmitting information from one device to another.

**Bus.** One or more conductors which are used as a path for transmitting information from any of several sources to any of several destinations.

Calculator. See Computer.

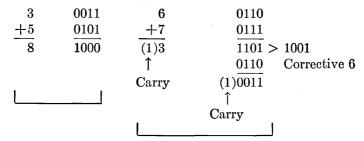

Carry. (1) A signal, or an expression, produced as a result of an arithmetic operation on one digit place of two or more numbers expressed in positional notation, and transferred to the next higher place for processing there. (2) Usually a signal, or an expression, as defined in (1) which arises, in adding, when the sum of two digits in the same digit place equals or exceeds the base of the number system in use. If a carry into a digit place will result in a carry out of the same digit place, and if the normal adding circuit is bypassed when generating this new carry, it is called a standing-on-nines carry, or high-speed carry. If the normal adding circuit is used in such a case, the carry is called a cascaded carry. If a carry resulting from the addition of carries is not allowed to propagate (e.g., when forming the partial product in one step of a multiplication process), the process is called a partial carry. If it

is allowed to propagate, the process is called a **complete carry**. If a carry generated in the most significant digit place is sent directly to the least significant digit place (e.g., when adding two negative numbers by using nines complements) that carry is called an **end-around carry**. (3) In direct subtraction, a signal or expression as defined in (1) which arises when the difference between the digits is less than zero. Such a carry is frequently called a **borrow**. (4) The action of forwarding a carry. (5) The command requesting a carry to be forwarded.

Cascaded Carry. See Carry.

Cell. An elementary unit of storage (e.g., binary cell, decimal cell).

**Channel.** That portion of a storage medium which is accessible to a given reading station. See also *Track*.

**Character.** One of a set of elementary marks or events which may be combined to express information. *Note*. A group of characters, in one context, may be considered as a single character in another, as in the binary-coded-decimal system.

**Check.** A process of partial or complete testing of (a) the correctness of machine operations, (b) the existence of certain prescribed conditions within the computer, or (c) the correctness of the results produced by a routine. A check of any of these conditions may be made automatically by the equipment or may be programmed. See also *Verification*.

Check, Automatic. A check performed by equipment built into the computer specifically for that purpose, and automatically accomplished each time the pertinent operation is performed. Sometimes referred to as a built-in check. Machine check can refer to an automatic check, or to a programmed check of machine functions.

Check Digits. See Check, Forbidden Combination.

Check, Forbidden Combination. A check (usually an automatic check) which tests for the occurrence of a nonpermissible code expression. A self-checking code (or error-detecting code) uses code expressions such that one (or more) error(s) in a code expression produces a forbidden combination. A parity check makes use of a self-checking code employing binary digits in which the total number of 1's (or 0's) in each permissible code expression is always odd or always even. A check may be made for either even parity or odd parity. A redundancy check employs a self-checking code which makes use of redundant digits called check digits.

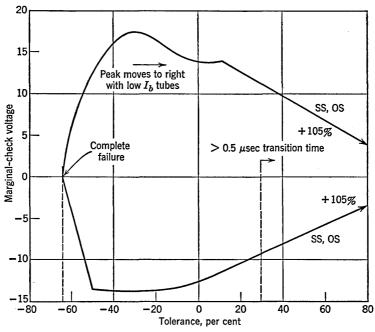

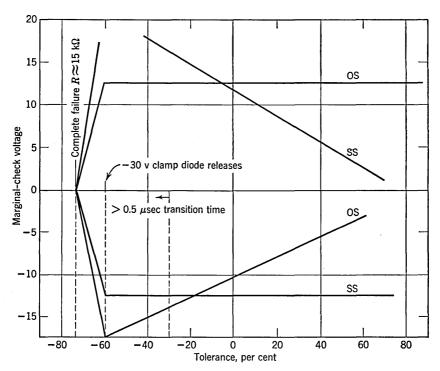

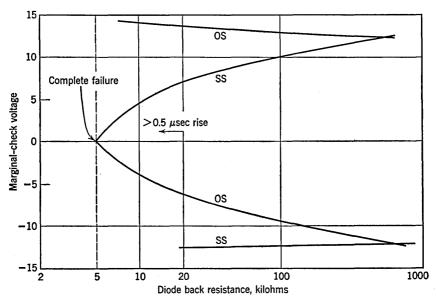

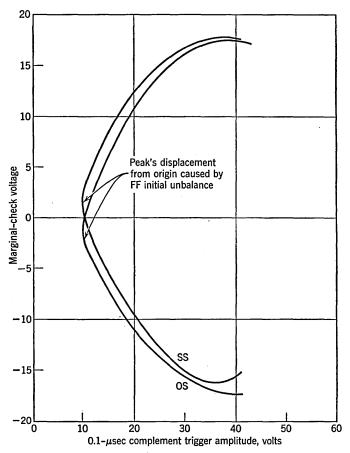

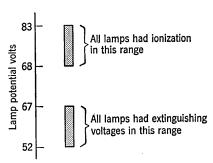

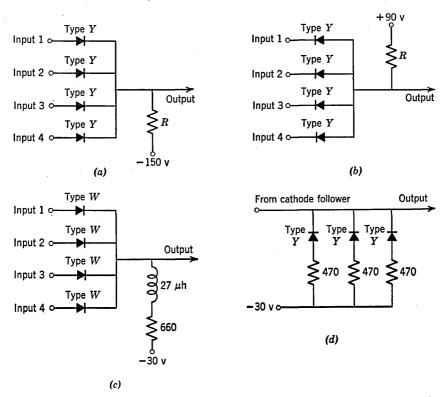

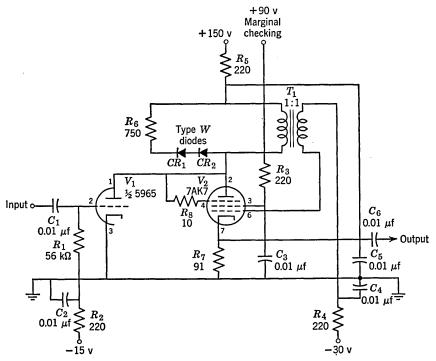

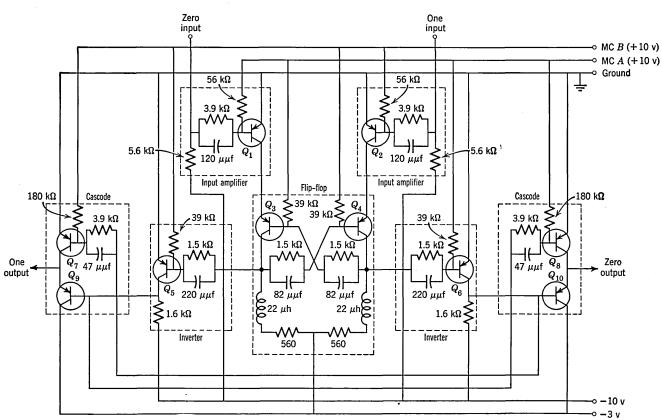

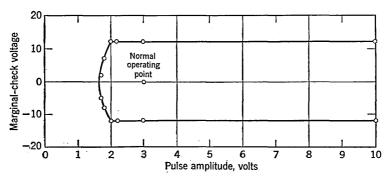

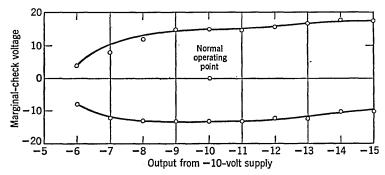

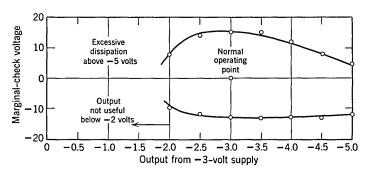

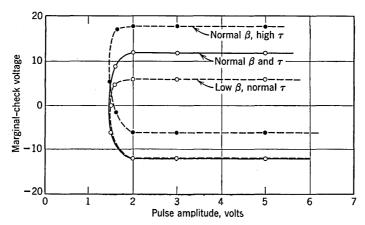

Check, Marginal. A preventive maintenance procedure in which certain operating conditions, e.g., supply voltage or frequency, are varied about their normal values in order to detect and locate incipient defective units.

Check Problem. See Check, Programmed.

Check, Programmed. A check consisting of tests inserted into the programmed statement of the problem and accomplished by appropriate use of the machine's instructions. A mathematical check (or control) is a programmed check of a sequence of operations which makes use of the mathematical properties of that sequence. A check routine or check problem is a routine or problem which is designed primarily to indicate whether a fault exists in the computer, without giving detailed information on the location of the fault. See also Diagnostic Routine and Test Routine under Routine.

Check Routine. See Check, Programmed.