---

# DSD 480

---

**DATA SYSTEMS DESIGN**

DSD 480

FLEXIBLE DISK SYSTEM

INSTALLATION AND PROGRAMMING MANUAL

Data Systems Design, Inc.

2241 Lundy Avenue

San Jose, CA 95131

Copyright 1983

All rights reserved. No part of this manual

may be reproduced in any form or by any

means without prior written permission of

Data Systems Design.

## WARRANTY STATEMENT

Data Systems Design's products are warranted against defects in materials and workmanship. For DSD products sold in the U.S.A., this warranty applies for ninety (90) days from date of shipment.\* DSD will, at its option, repair or replace either equipment or components which prove to be defective during the warranty period. This warranty includes labor, parts and surface travel costs of system modules or components. Freight charges for other than surface travel or for complete systems returned for repair are not included in this warranty. Equipment returned to DSD for repair must be shipped freight prepaid and accompanied by a Material Return Authorization number issued by DSD. Repairs necessitated by shipping damage, misuse of the equipment, or by hardware, software, or interfacing not provided by DSD are not covered by this warranty.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. DSD SHALL NOT BE LIABLE FOR CONSEQUENTIAL DAMAGES.

NOTE: ORDERS SHOULD BE PLACED THROUGH THE NEAREST REGIONAL SALES OFFICE.

EASTERN REGION SALES

51 Morgan Drive

Norwood, MA 02062

TEL: (617)769-7620

TWX: 710-336-0120

WESTERN REGION SALES

2560 Mission College Boulevard

Suite 108

Santa Clara, CA 95051

TEL: (408)727-3163

CENTRAL REGION SALES

5050 Quorum Drive

Suite 339

Dallas, TX 75240

(214)980-4884

CORPORATE HEADQUARTERS

2241 Lundy Avenue

San Jose, CA 95131

\* For products sold outside the U.S.A., contact your local Data Systems Design distributor for warranty terms.

## PREFACE

The material in this manual is subject to change without notice. The manufacturer assumes no responsibility for any errors which may appear in this manual.

Please note that DEC, PDP, RT-11, and UNIBUS are registered trademarks of the Digital Equipment Corporation.

## SAFETY

Operating and maintenance personnel must at all times observe sound safety practices. Do not replace components, or attempt repairs to this equipment with the power turned on. Under certain conditions, dangerous voltage potentials may exist when the power switch is in the off position, due to charges retained by capacitors. To avoid injury, always remove power cord before attempting repair procedures.

Data Systems Design, Inc. will accept no responsibility or liability for injury or damage sustained as a result of operation or maintenance of this equipment with the covers removed and power applied.

## CAUTION

This equipment had been tested with a class A computing device and has been found to comply with Part 15 of FCC Rules. See instruction manual. Operation in a residential area may cause unacceptable interference to radio and TV reception requiring the operator to take what ever steps are necessary to correct the interference.

## TABLE OF CONTENTS

|                                                   | <u>Page</u> |

|---------------------------------------------------|-------------|

| <b>CHAPTER 1: <u>GENERAL INFORMATION</u></b>      |             |

| Data Sheet                                        | 1-1         |

| Introduction                                      | 1-1         |

| Controller/Formatter Module                       | 1-1         |

| Disk Drives                                       | 1-1         |

| Computer Interface Card                           | 1-1         |

| Power Supply                                      | 1-2         |

| Interconnecting Cable                             | 1-2         |

| <b>CHAPTER 2: <u>INSTALLATION</u></b>             |             |

| Unpacking and Inspection                          | 2-1         |

| Power Requirements                                | 2-1         |

| Operational Environment                           | 2-3         |

| Installing the DSD 480 Chassis                    | 2-3         |

| Installing the DSD 480 Interface Module and Cable | 2-6         |

| LSI-11 Based Systems                              | 2-7         |

| PDP-11 Based Systems                              | 2-9         |

| Hardware Modes                                    | 2-16        |

| Mode 1 (RX01 Compatible)                          | 2-16        |

| Mode 2 (RX02 Compatible)                          | 2-16        |

| Mode 3 (Extended IBM)                             | 2-16        |

| Hyperdiagnostic™ Mode                             | 2-16        |

| Switch Selection of Proper Operating Mode         | 2-16        |

| <b>CHAPTER 3: <u>BASIC SYSTEM OPERATION</u></b>   |             |

| Applying ac Power                                 | 3-1         |

| Inserting a Diskette                              | 3-2         |

| Initialization Response Check                     | 3-3         |

| System Bootstrapping                              | 3-4         |

| Standard LSI-11 and PDP-11 Systems                | 3-4         |

| Non-Standard Device Addresses                     | 3-4         |

| ROM (Read Only Memory) Installed as Main Memory   | 3-5         |

| Bootstrapping Without System Test Functions       | 3-5         |

| Acceptance Testing                                | 3-6         |

## TABLE OF CONTENTS (Cont)

|                                                                       | <u>Page</u> |

|-----------------------------------------------------------------------|-------------|

| <b>CHAPTER 4: <u>SOFTWARE</u></b>                                     |             |

| Operating Modes                                                       | 4-1         |

| Diskette Compatibility                                                | 4-1         |

| DEC-Compatible Modes                                                  | 4-3         |

| Single-Sided Operation                                                | 4-3         |

| Double-Sided Operation                                                | 4-3         |

| Single-Density Diskettes in a Double Density RX02 - Compatible System | 4-4         |

| RX02 - Compatible System                                              | 4-4         |

| IBM 2D-256 Compatibility in Mode 2                                    | 4-4         |

| Mode 3                                                                | 4-4         |

| Programming Interface                                                 | 4-4         |

| DEC II Family                                                         | 4-5         |

| Mode 1 (RX01 Compatible) Operation                                    | 4-6         |

| Peripheral Device Registers                                           | 4-6         |

| Mode 1 Protocols                                                      | 4-11        |

| Typical Sequences of Operation                                        | 4-17        |

| Common Programming Mistakes                                           | 4-20        |

| Mode 2 (RX02 Compatible) Operation                                    | 4-21        |

| Peripheral Device Registers                                           | 4-21        |

| Mode 2 Protocols                                                      | 4-29        |

| Typical Sequence of Operations                                        | 4-36        |

| Common Programming Mistakes                                           | 4-39        |

| Mode 3 (Extended IBM)                                                 | 4-40        |

| Peripheral Device Registers                                           | 4-40        |

| Mode 3 Protocols                                                      | 4-48        |

| Diskette Formatting                                                   | 4-56        |

| Power Fail                                                            | 4-58        |

| <b>CHAPTER 5: <u>HARDWARE SELF-TESTING</u></b>                        |             |

| Automatic Self-Testing                                                | 5-1         |

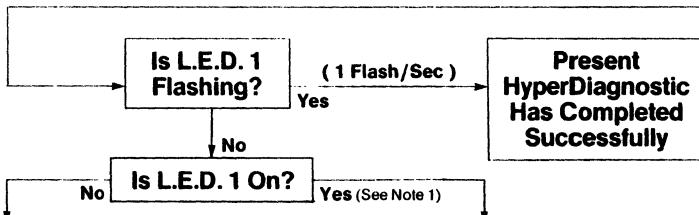

| User Selectable Self-Tests & HyperDiagnostics                         | 5-2         |

| Test Selection Indicator Lights and DIP Switch                        | 5-2         |

| Normal Mode                                                           | 5-6         |

| HyperDiagnostic Mode                                                  | 5-12        |

| Test Strategy Using HyperDiagnostics                                  | 5-16        |

| Individual HyperDiagnostic Tests                                      | 5-17        |

| <b>CHAPTER 6: <u>COMPUTER RESIDENT DIAGNOSTICS</u></b>                |             |

| Program Loading and Monitor Protocol                                  | 6-1         |

| FLPEXR Diagnostic Routines                                            | 6-2         |

## TABLE OF CONTENTS (Cont)

|                                          | <u>Page</u> |

|------------------------------------------|-------------|

| Mode Setting Commands                    | 6-6         |

| Format Initialization Commands           | 6-9         |

| Dump and Copy Utility Commands           | 6-10        |

| FLPEXR Program Status and Error Displays | 6-12        |

## CHAPTER 7: CUSTOMER SERVICE

|                           |     |

|---------------------------|-----|

| Service Procedure         | 7-1 |

| Customer Services         | 7-1 |

| Service Policy            | 7-2 |

| Material Return Procedure | 7-2 |

## APPENDICES

### APPENDIX A: STANDARD JUMPER POSITIONS ON INTERFACE AND CONTROLLER MODULES

|                                 |     |

|---------------------------------|-----|

| DSD 480 Controller Module       | A-1 |

| LSI-II Interface Card RX01 Mode | A-2 |

| LSI-II Interface Card RX02 Mode | A-3 |

| PDP-II Interface Card RX02 Mode | A-4 |

| PDP-II Interface Card RX01 Mode | A-5 |

### APPENDIX B: DISK DRIVE MAINTENANCE MANUAL

### APPENDIX C: FLEXIBLE DISKETTE DESCRIPTION AND MAINTENANCE

|                                        |     |

|----------------------------------------|-----|

| Diskette Description                   | C-1 |

| Industry Recording and Media Standards | C-3 |

| Diskette Care Guidelines               | C-7 |

| IBM Diskette Types                     | C-8 |

### APPENDIX D: LSI-II AND PDP-II BOOTSTRAP PROM PROGRAM

### APPENDIX E: CONTROLLER ERROR CODE DESCRIPTIONS AND CAUSES

## TABLE OF CONTENTS (Cont)

### Page

#### APPENDIX F: IMPLEMENTATION OF DOUBLE SIDED SUPPORT FOR THE DSD 480

|                                         |     |

|-----------------------------------------|-----|

| Double-Sided Support Under RT-II        | I-1 |

| Double-Sided Support Under RSX-II M     | I-1 |

| The DSD Monitor Patch Program for RT-II | I-1 |

### FIGURES

| <u>Figure No.</u> | <u>Description</u>                                                       | <u>Page</u> |

|-------------------|--------------------------------------------------------------------------|-------------|

| 2-1               | AC Power Connector Assembly                                              | 2-2         |

| 2-2               | Chassis Slides Mounting                                                  | 2-4         |

| 2-3               | Securing the DSD 480 in a Rack                                           | 2-5         |

| 2-4               | Front View of Chassis With Front Panel Removed to Show<br>Securing Holes | 2-6         |

| 2-5               | LSI-II Computer Interface Diagram                                        | 2-8         |

| 2-6               | Option Priority in LSI-II Backplane                                      | 2-10        |

| 2-7               | PDP-II Computer Interface Card Diagram                                   | 2-11        |

| 2-8               | PDP-II Interrupt Priority Levels                                         | 2-13        |

| 2-9               | PDP-II Interrupt Priority Jumper Diagram                                 | 2-14        |

| 2-10              | Typical UNIBUS Hex Backplane                                             | 2-15        |

| 2-11              | Controller/Formatter Module DIP-Switch                                   | 2-17        |

| 2-12              | Controller DIP-Switch Settings: Normal Modes                             | 2-19        |

| 3-1               | Back Panel of DSD 480                                                    | 3-1         |

| 3-2               | Orientation of Diskette For Insertion                                    | 3-2         |

| 4-1               | Mode 1 Register Formats                                                  | 4-10        |

| 4-2               | Mode 2 Command and Status Register Format                                | 4-22        |

| 4-3               | Mode 2 Register Formats                                                  | 4-28        |

| 4-4               | Mode 3 Command and Status Register Format                                | 4-42        |

| 4-5               | Mode 3 Register Formats                                                  | 4-47        |

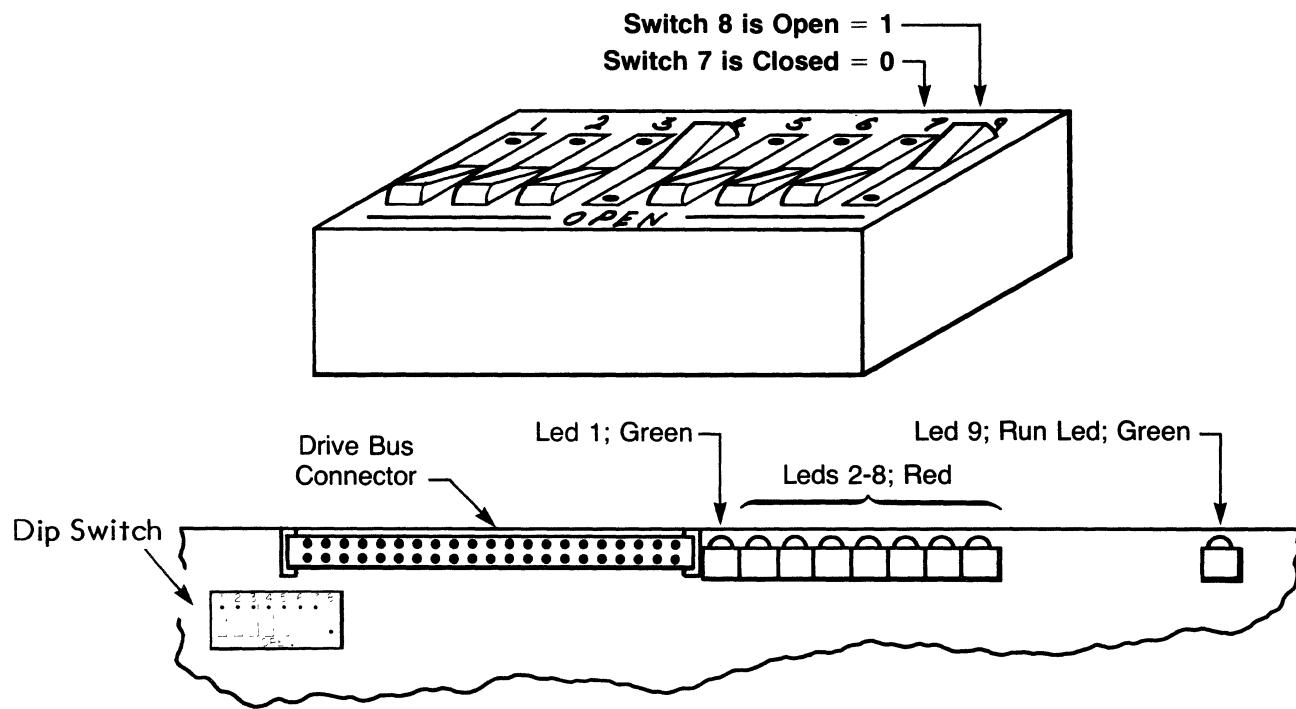

| 5-1               | Controller Module Indicator Lights and<br>DIP-Switch Orientation         | 5-3         |

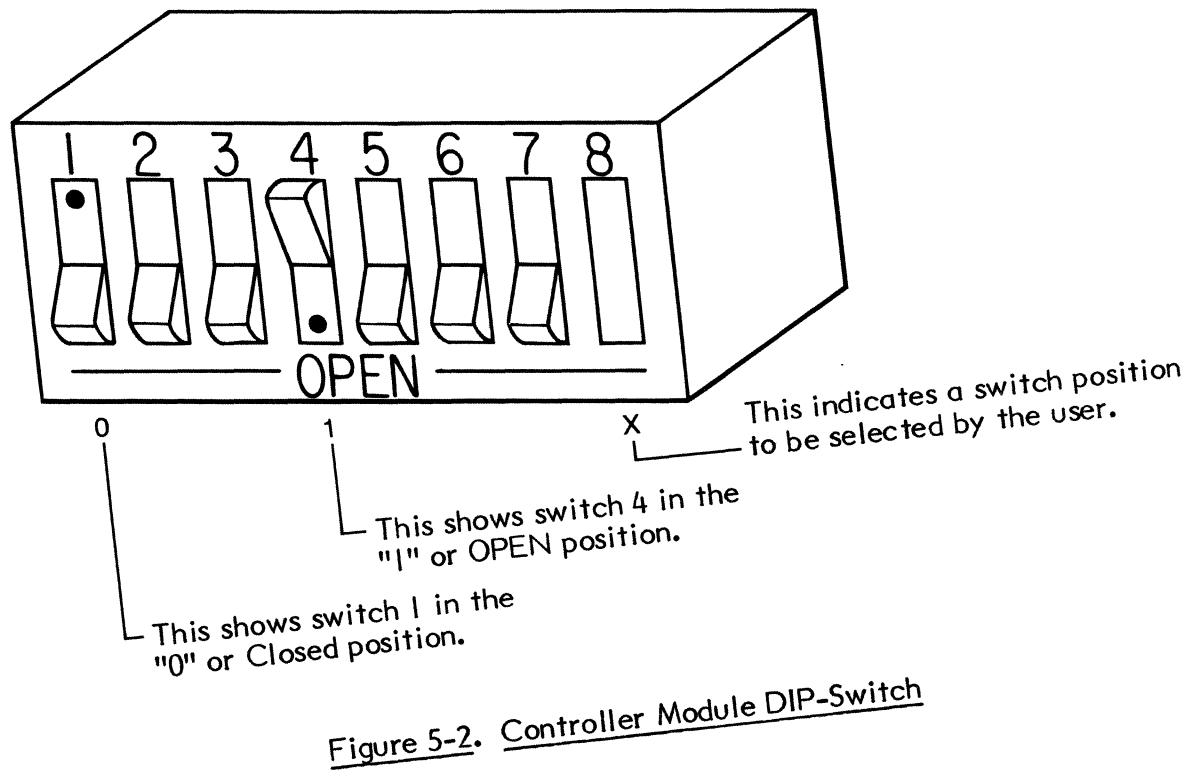

| 5-2               | Controller Module DIP-Switch                                             | 5-4         |

| 5-3               | Controller DIP-Switch Functions                                          | 5-5         |

| 5-4               | Controller DIP-Switch Settings                                           | 5-6         |

| 5-5               | Controller LED Decoding Chart                                            | 5-8         |

| 5-6               | Controller DIP-Switch Settings; Normal Mode                              | 5-9         |

### TABLES

| <u>Table No.</u> | <u>Description</u>                      |      |

|------------------|-----------------------------------------|------|

| 2-1              | LSI-II Register and Boot PROM Addresses | 2-7  |

| 2-2              | Controller and DIP-Switch Functions     | 2-18 |

## TABLE OF CONTENTS (Cont)

### TABLES (Cont)

| <u>Table No.</u> | <u>Description</u>                                                                                | <u>Page</u> |

|------------------|---------------------------------------------------------------------------------------------------|-------------|

| 4-1              | DEC and IBM Diskette Formats                                                                      | 4-2         |

| 4-2              | Mode 1 Command and Status Register                                                                | 4-9         |

| 4-3              | Mode 1 Error Register Codes (RXER)                                                                | 4-16        |

| 4-4              | Fill/Empty RX01 Sector Buffer Example                                                             | 4-19        |

| 4-5              | Read/Write/Write Deleted Data RX01 Sector Example                                                 | 4-35        |

| 4-6              | Modes 2 and 3 Definitive Error Codes                                                              | 4-36        |

| 4-7              | Fill/Empty RX02 Sector Buffer Example                                                             | 4-38        |

| 4-8              | Read/Write RX02 Sector Example                                                                    | 4-55        |

| 4-9              | Diskette Format Codes                                                                             | 4-55        |

| 5-1              | LED Error Class Codes in Normal Mode                                                              | 5-10        |

| 5-2              | Error Register Codes                                                                              | 5-11        |

| 5-3              | HyperDiagnostic Error Code Interpretations                                                        | 5-14        |

| 5-4              | Interpretation of LEDs 5, 6, 7, and 8 During Execution<br>of HyperDiagnostics while RUN LED is ON | 5-17        |

## CHAPTER I

### INTRODUCTION

The DSD 480 is an advanced double sided, double density flexible disk system for use with LSI-11 and PDP-11 computers. A complete system contains a chassis with two double sided disk drives, controller/formatter electronics and power supply, a separate interface card for LSI-11 or PDP-11 computers, interconnecting cables, a diagnostic diskette, and complete documentation. The system components are described below.

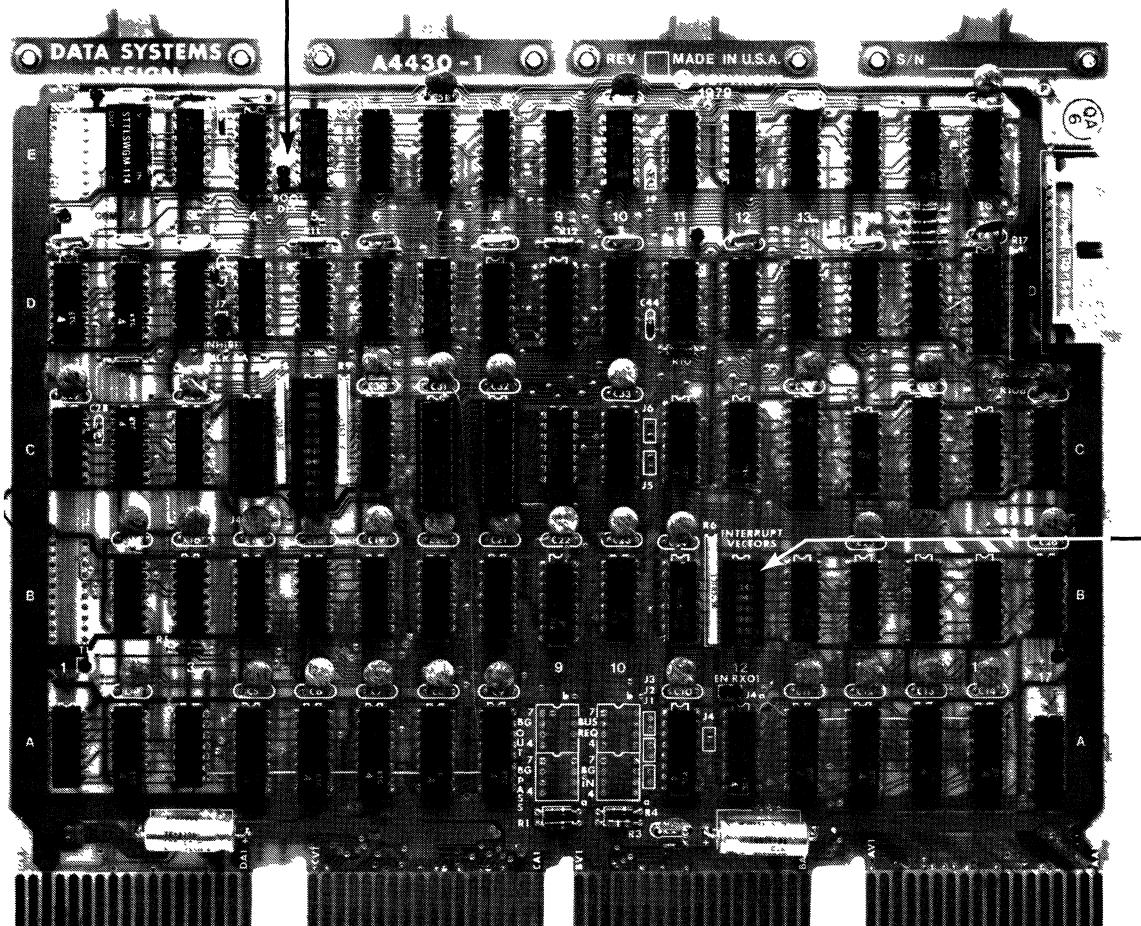

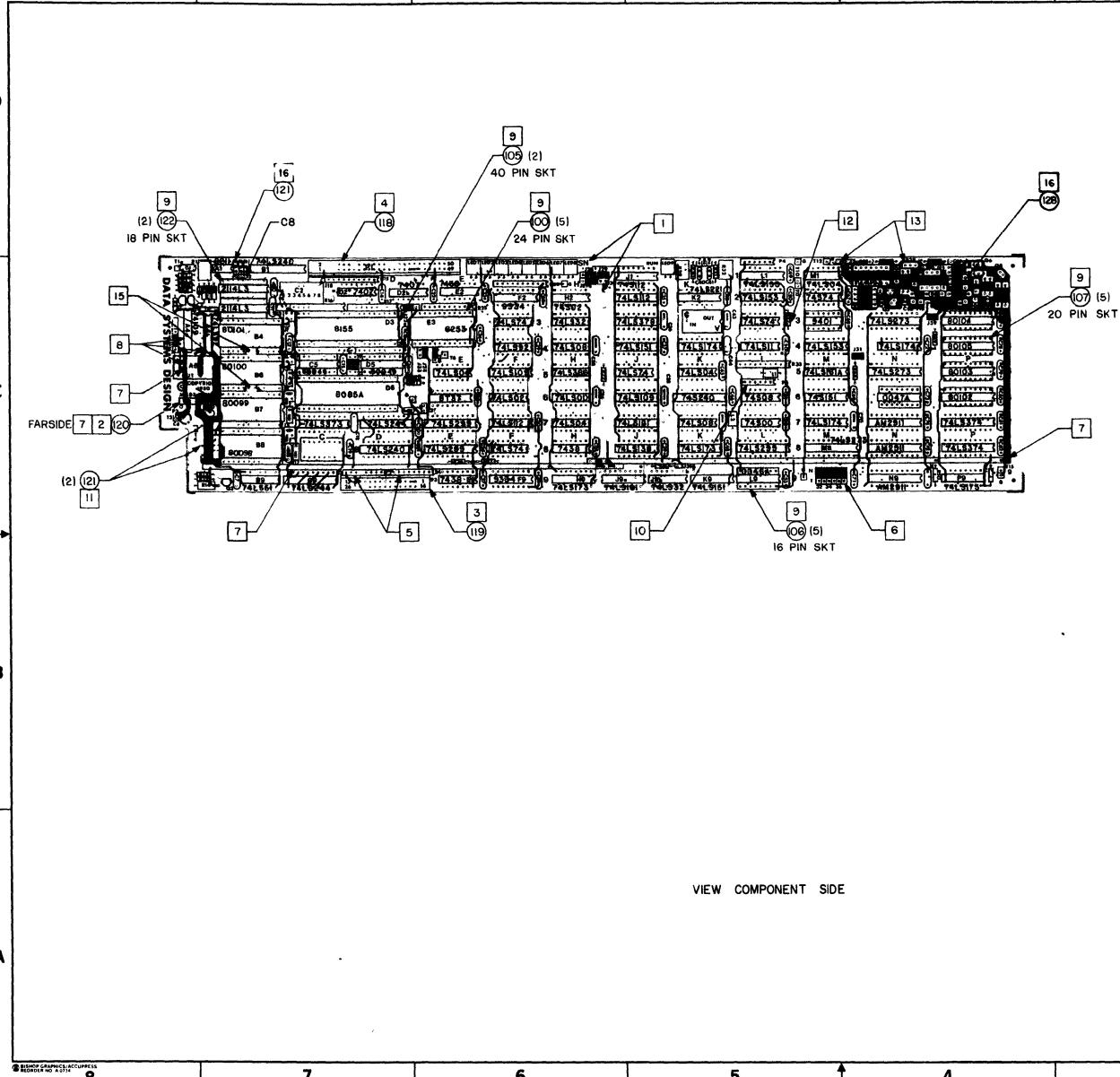

### CONTROLLER/FORMATTER MODULE

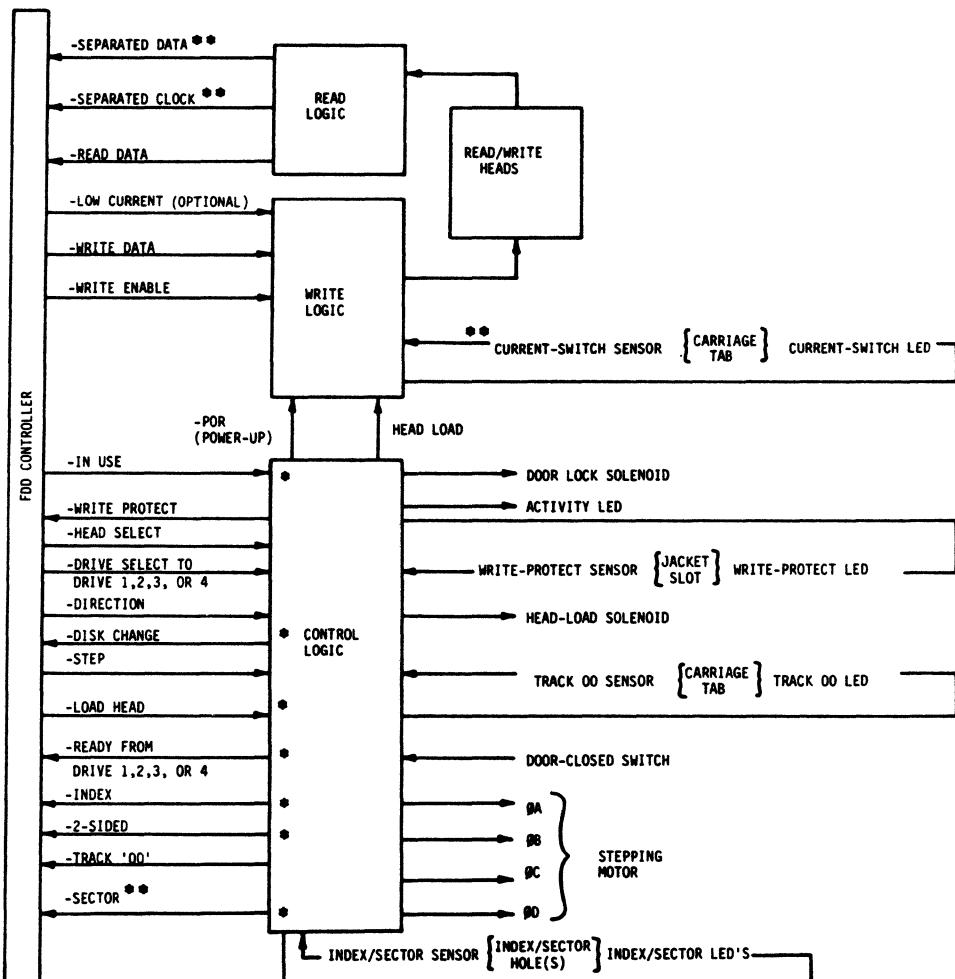

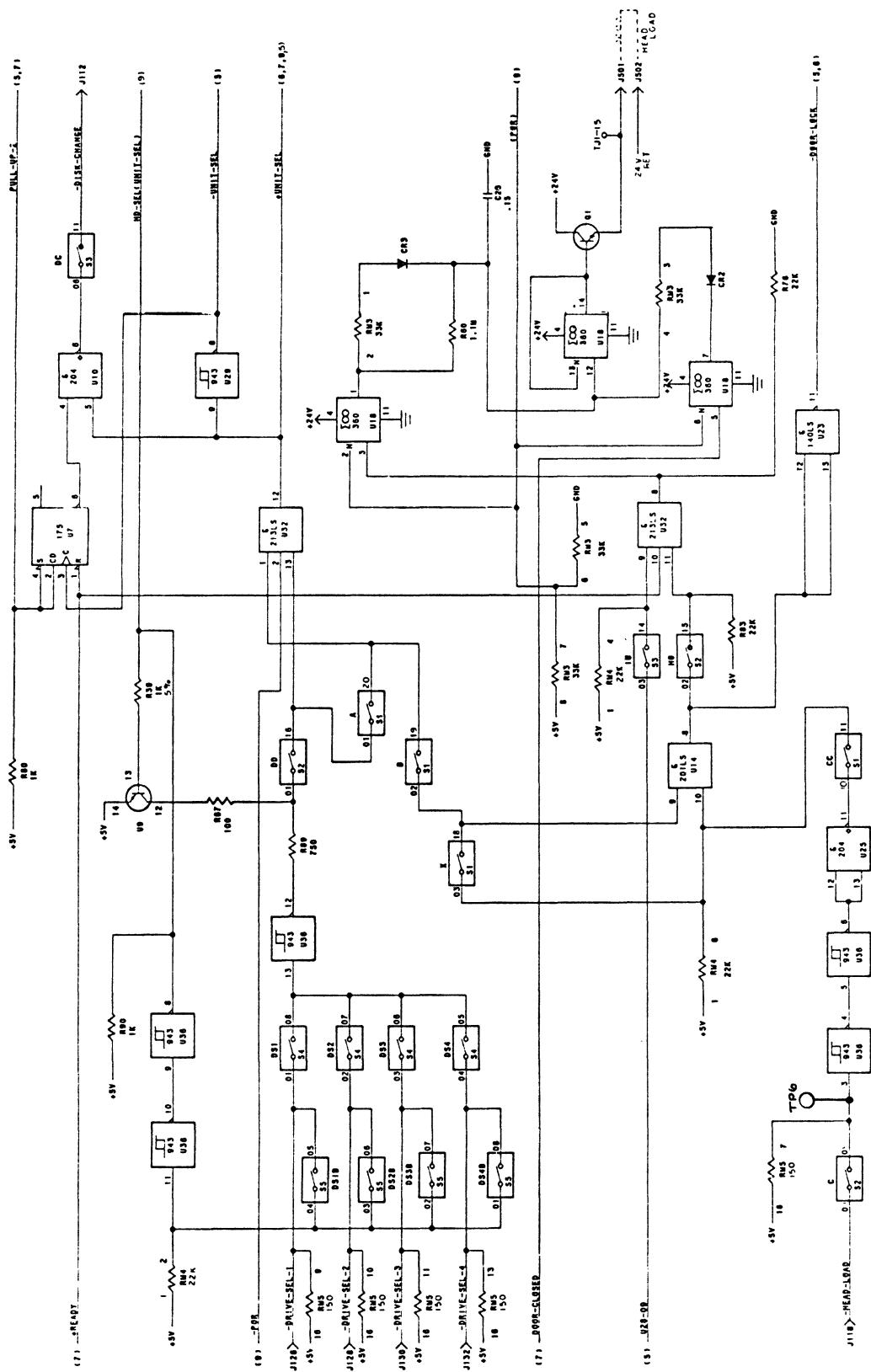

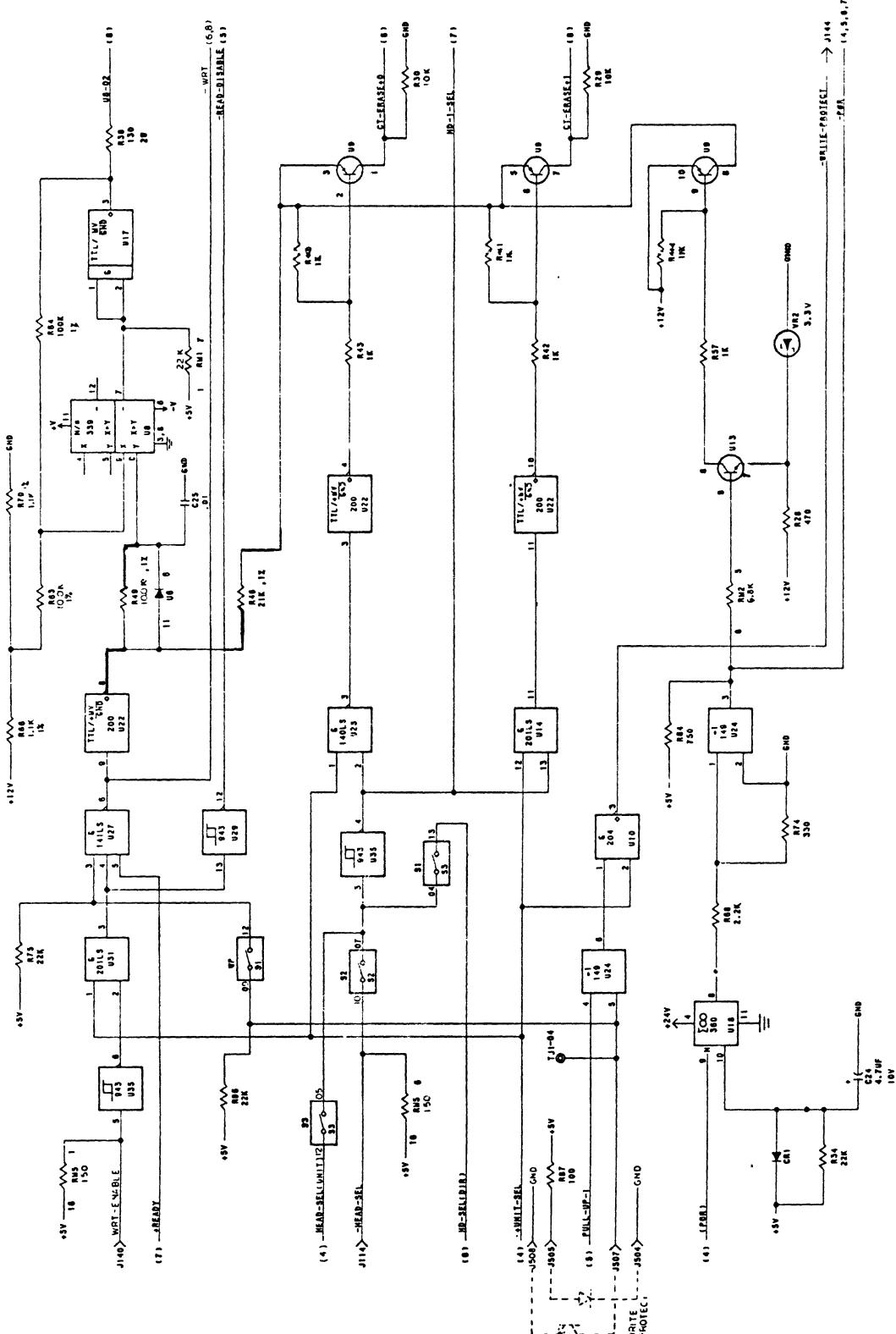

The intelligence of the DSD 480 resides in the microcode of the controller/formatter module. It accepts commands sent across the interface cable and controls the operation of the disk drives.

This module contains a microprogrammed read/write controller and an 8-bit microprocessor. The interface/controller module is connected to the disk drives, the interface bus connector, and the power distribution assembly.

Near the top of the controller/formatter module is a set of eight switches mounted in a dual in-line package (DIP). These switches are used to establish different system configurations and to specify the self-contained "HYPERDIAGNOSTICS" used during maintenance operations. Located near the switch is a row of eight LED indicator lights which help you interpret the status of "HYPERDIAGNOSTICS" operation. Appendix A contains information about the standard jumper positions in this controller.

The controller/formatter is capable of formatting diskettes in any DEC or IBM format. This capability allows you to recover diskettes with altered formatting information. It also allows you to select a sequential interleave data pattern which may improve your system's throughput.

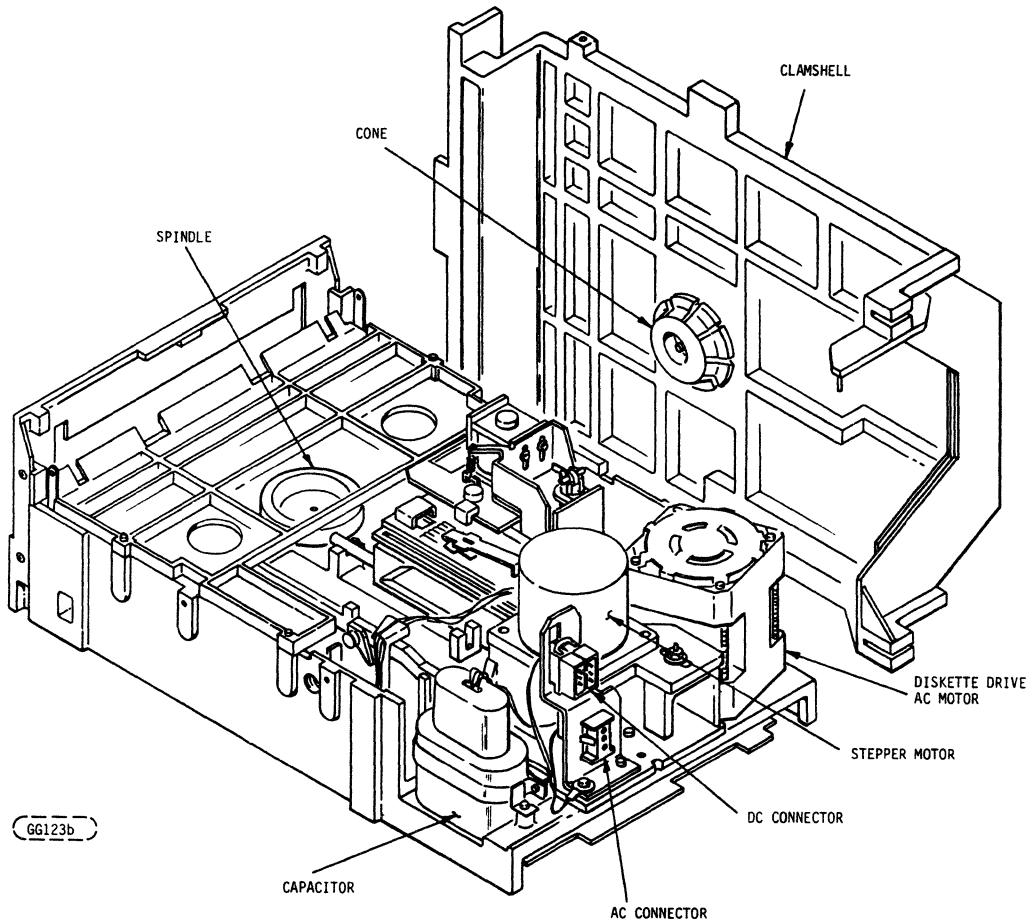

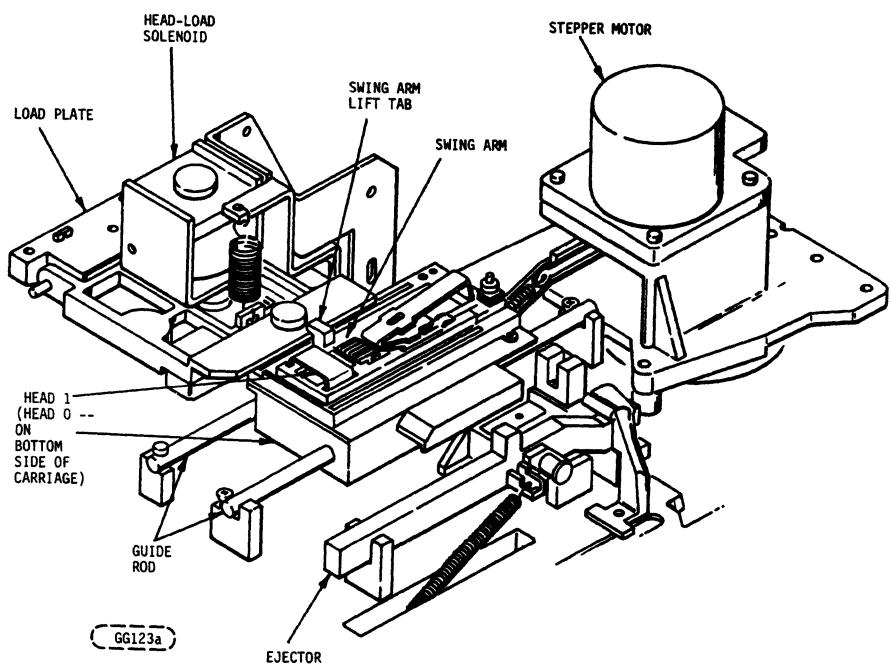

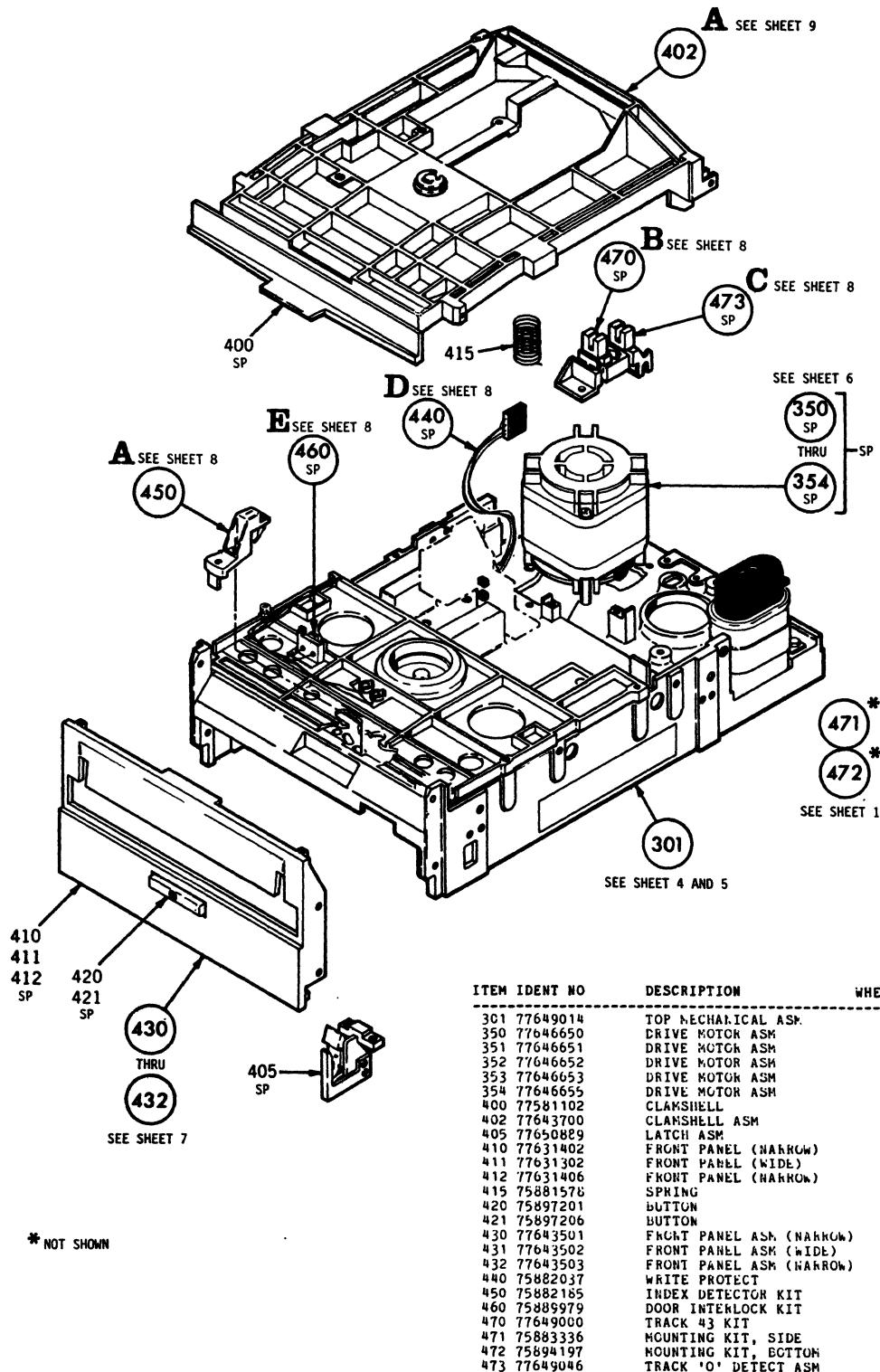

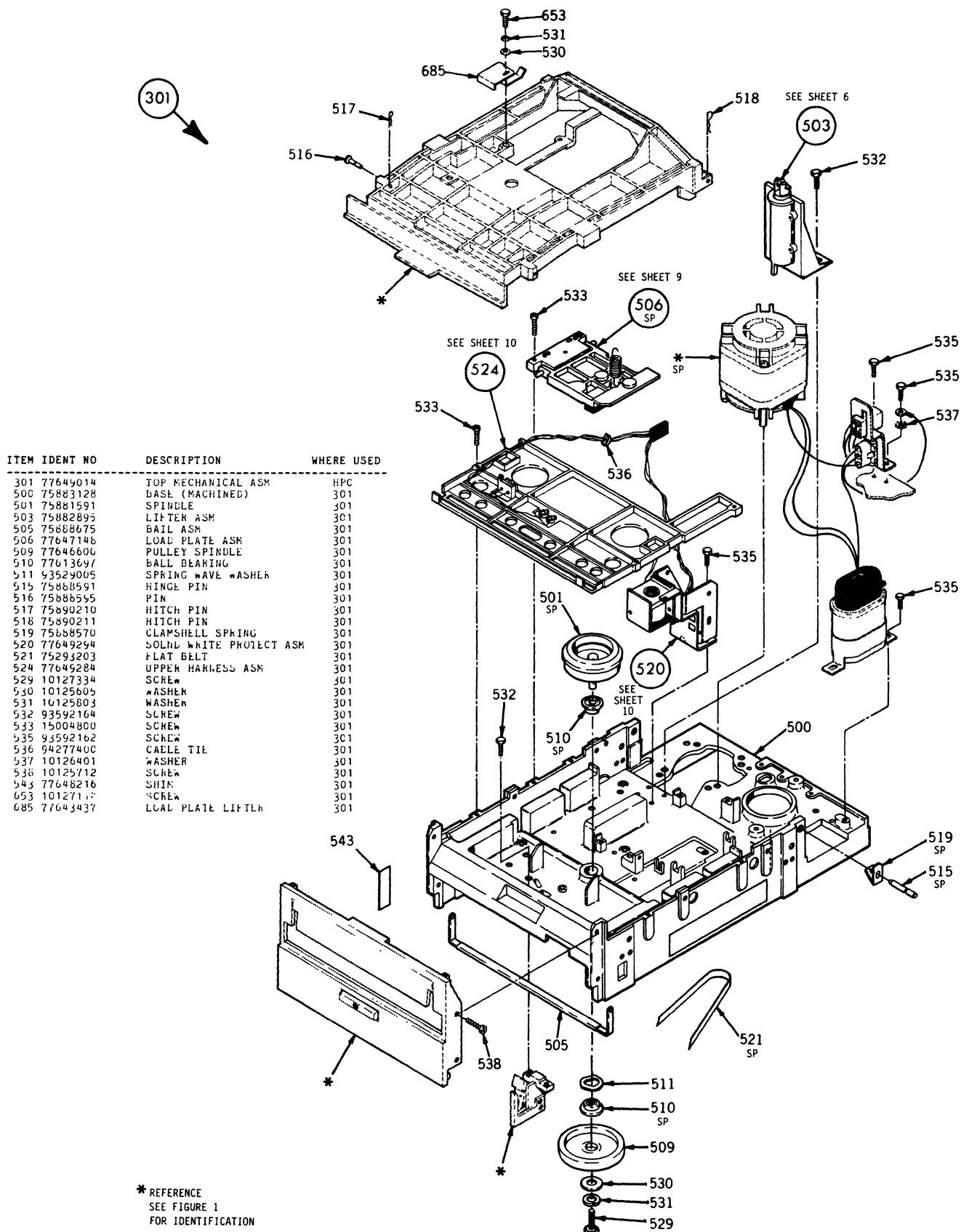

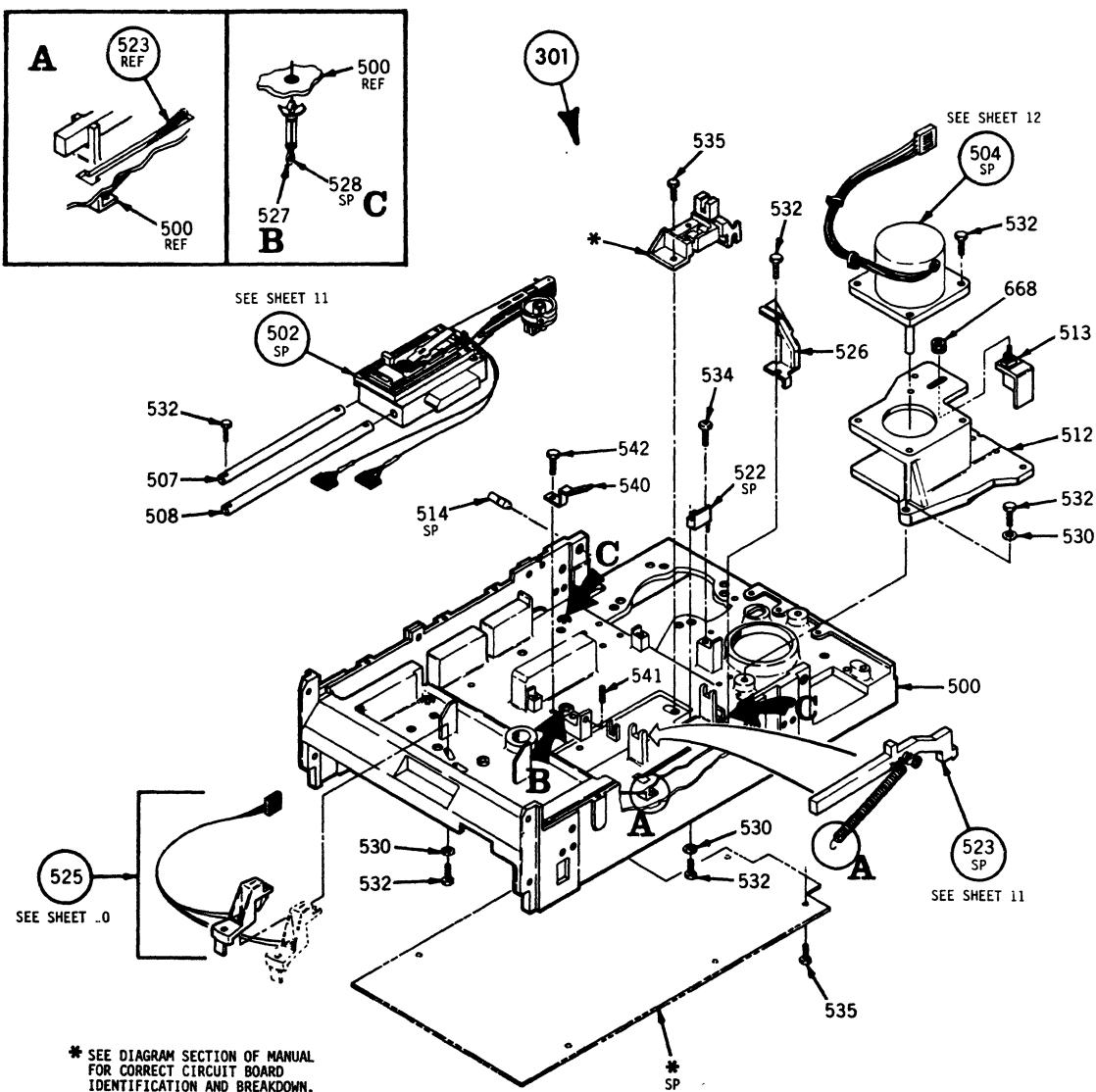

### DISK DRIVES

The DSD 480 is equipped with two double-sided disk drives installed in the chassis. The drives write data or retrieve data from the flexible disks.

The drives used in the DSD 480 each consist of read/write and control electronics, read/write heads, a head positioning mechanism and a drive motor.

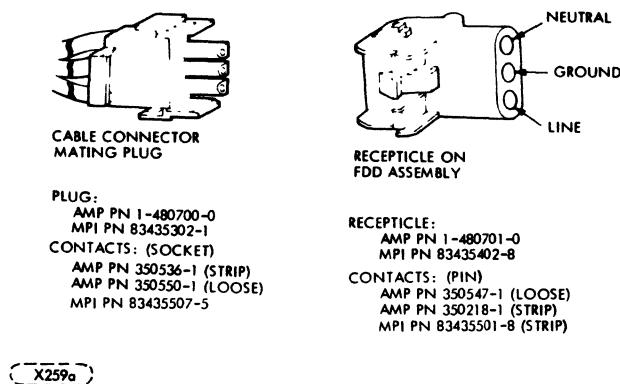

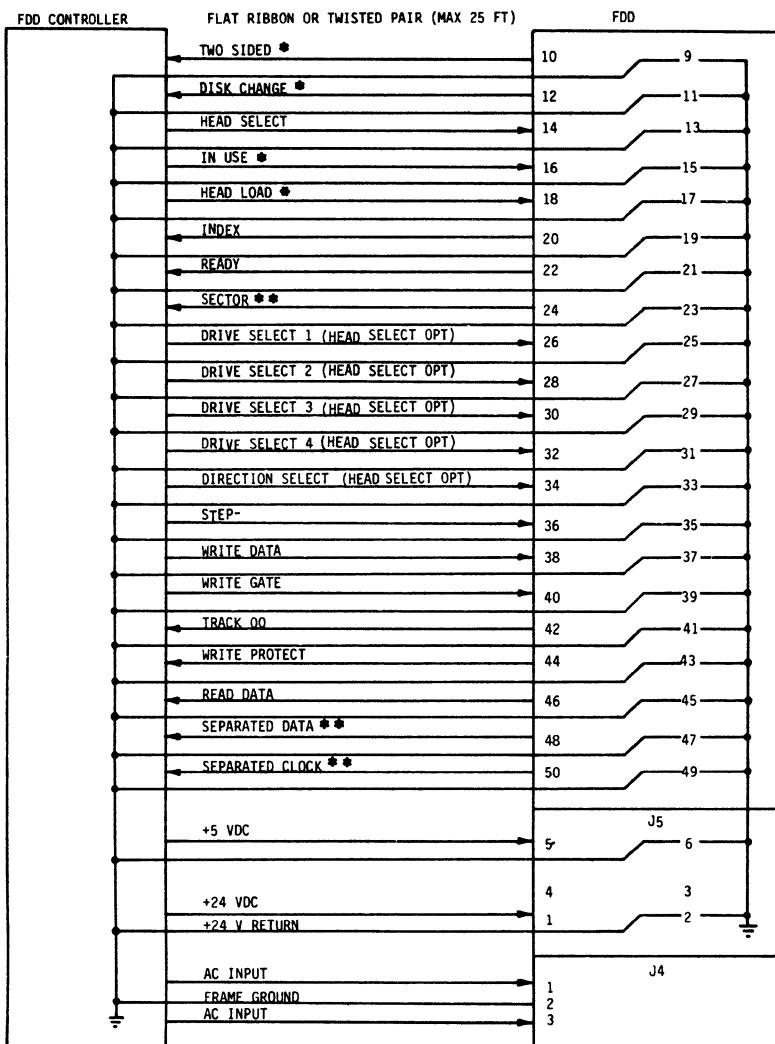

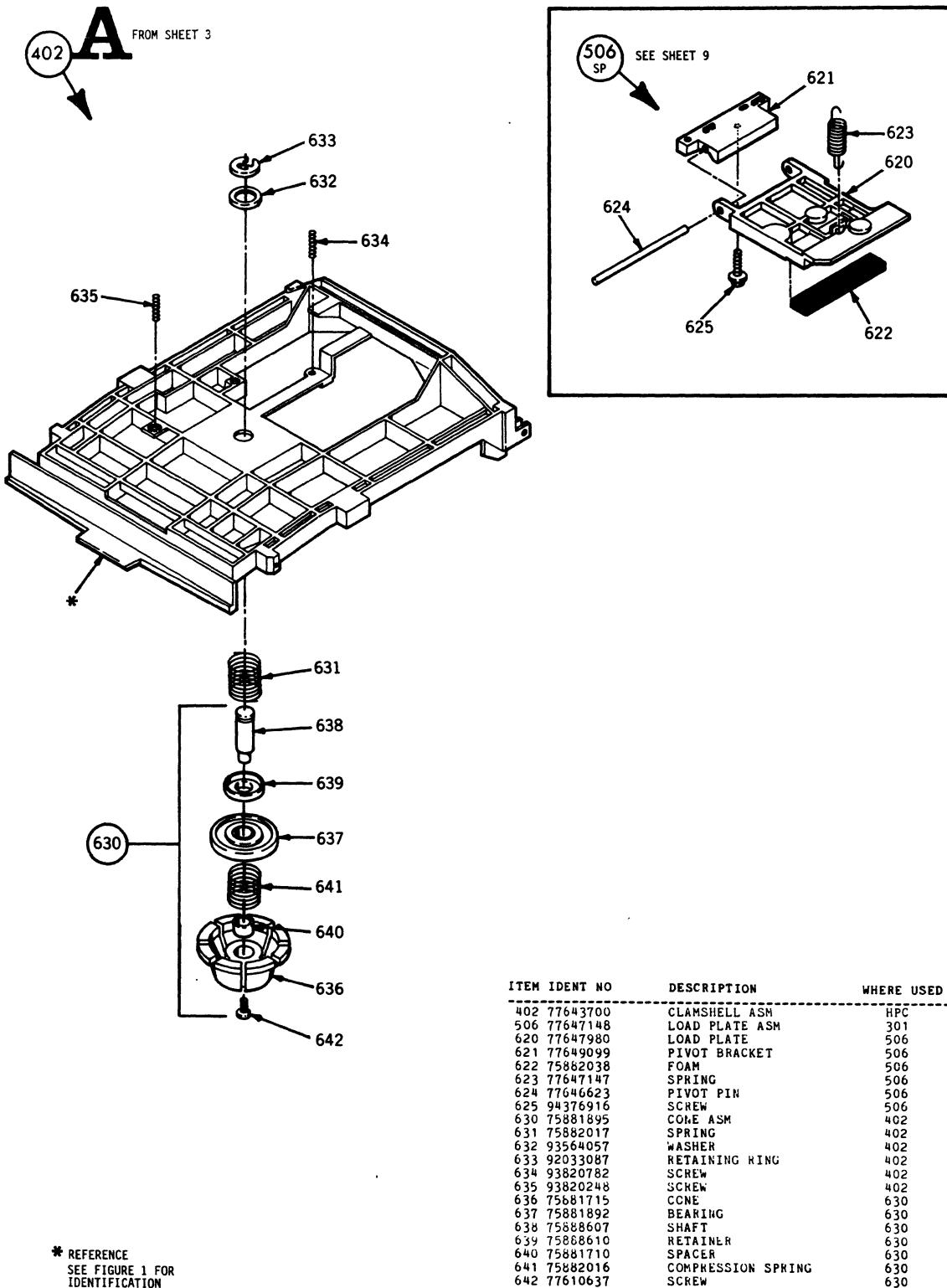

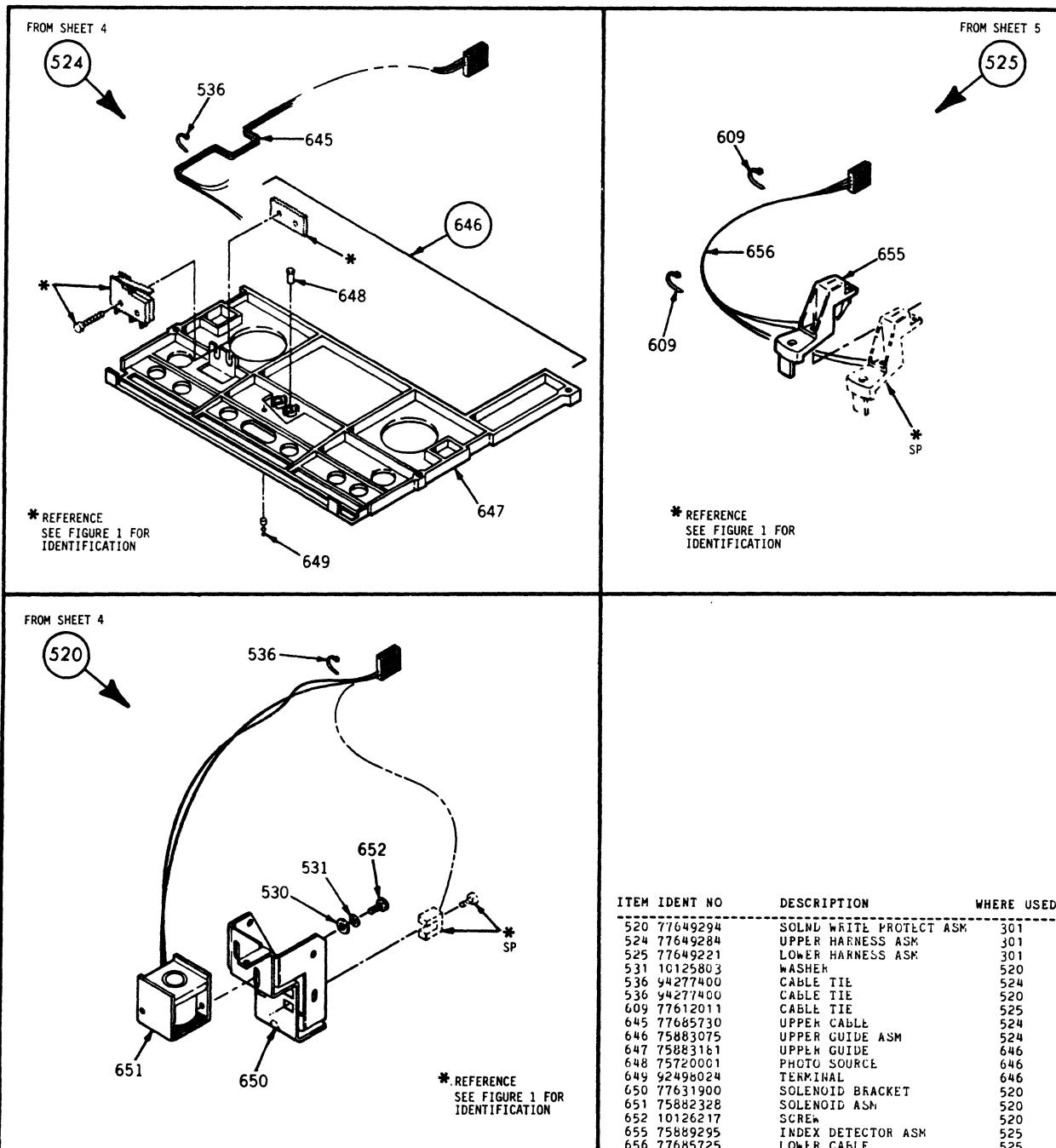

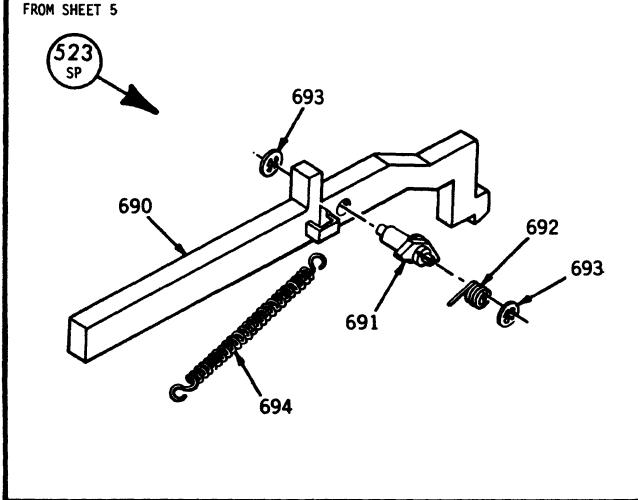

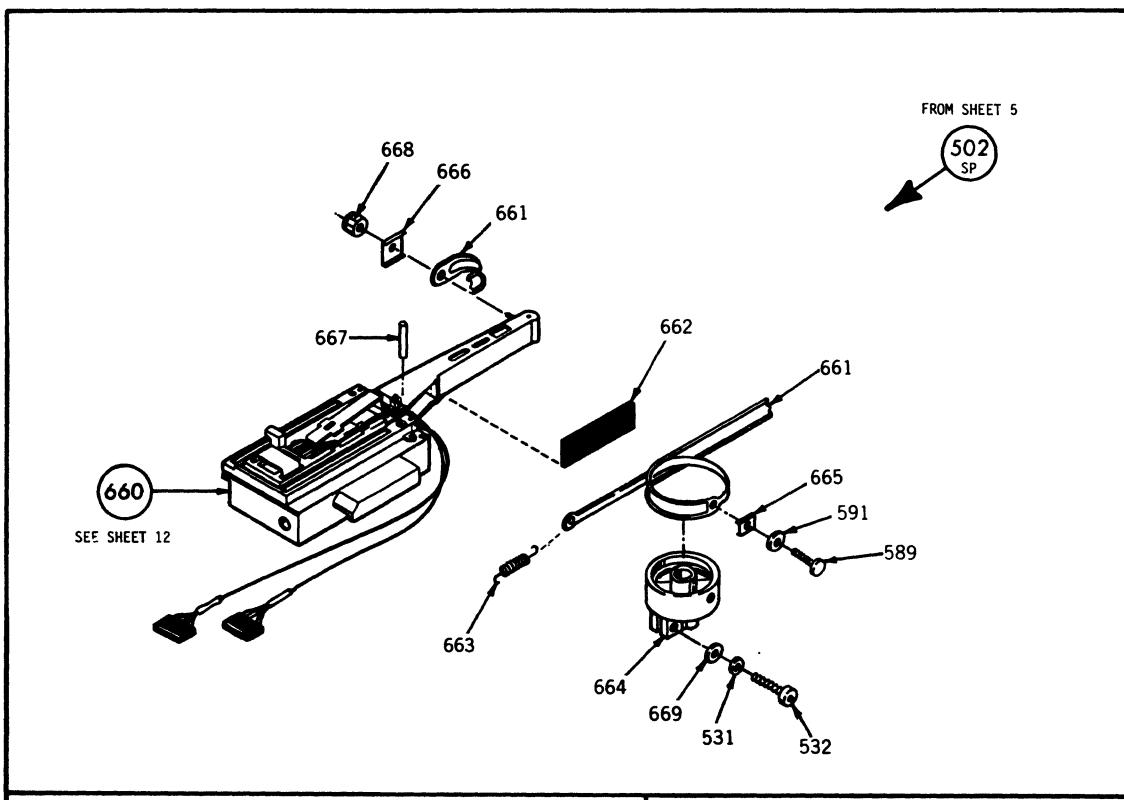

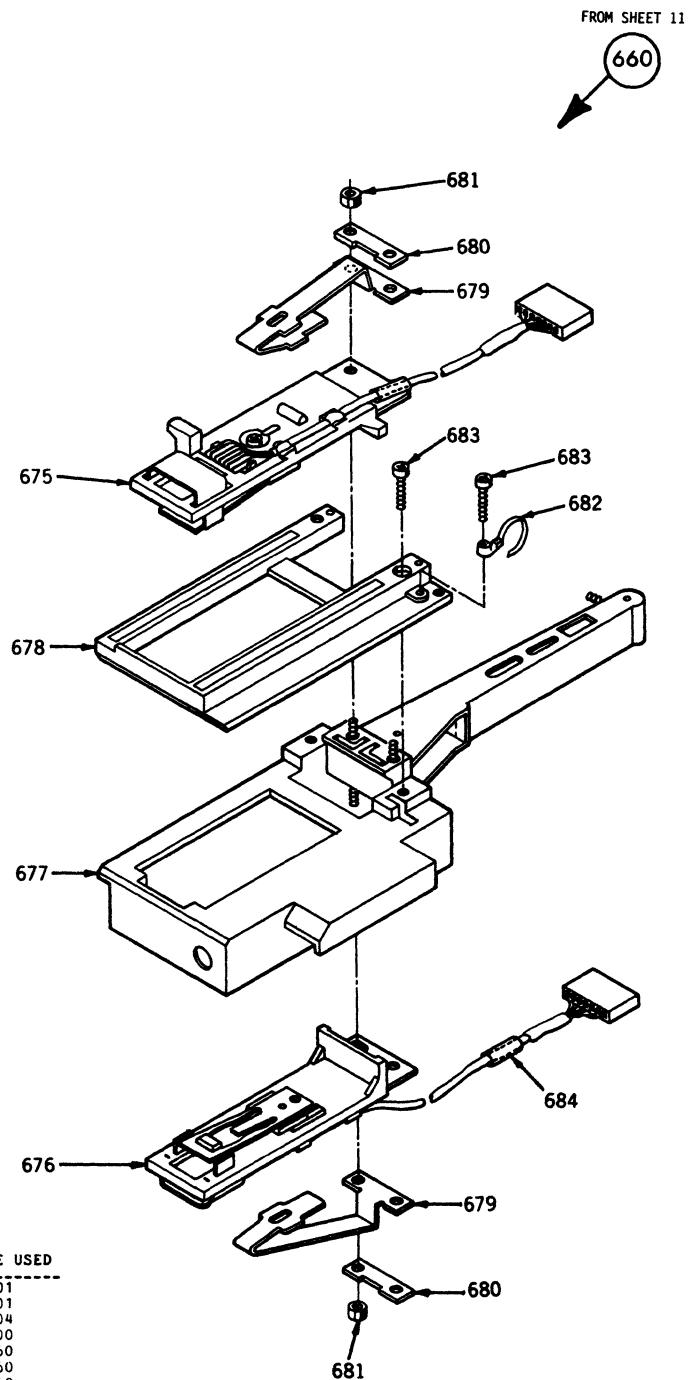

Each drive is fastened to the DSD 480 chassis by four screws accessible from the underside of the chassis. A 50-conductor flat-ribbon cable connects the controller module to the drives. Two additional cables provide AC and DC power to the connectors on each drive. Appendix B contains a copy of the maintenance manual published by the drive manufacturer.

## COMPUTER INTERFACE CARD

The computer interface card is a printed circuit board that accepts commands from the computer and passes them to the controller/formatter module. Data Systems Design manufactures interface modules for the DEC LSI-11 and PDP-11 computers.

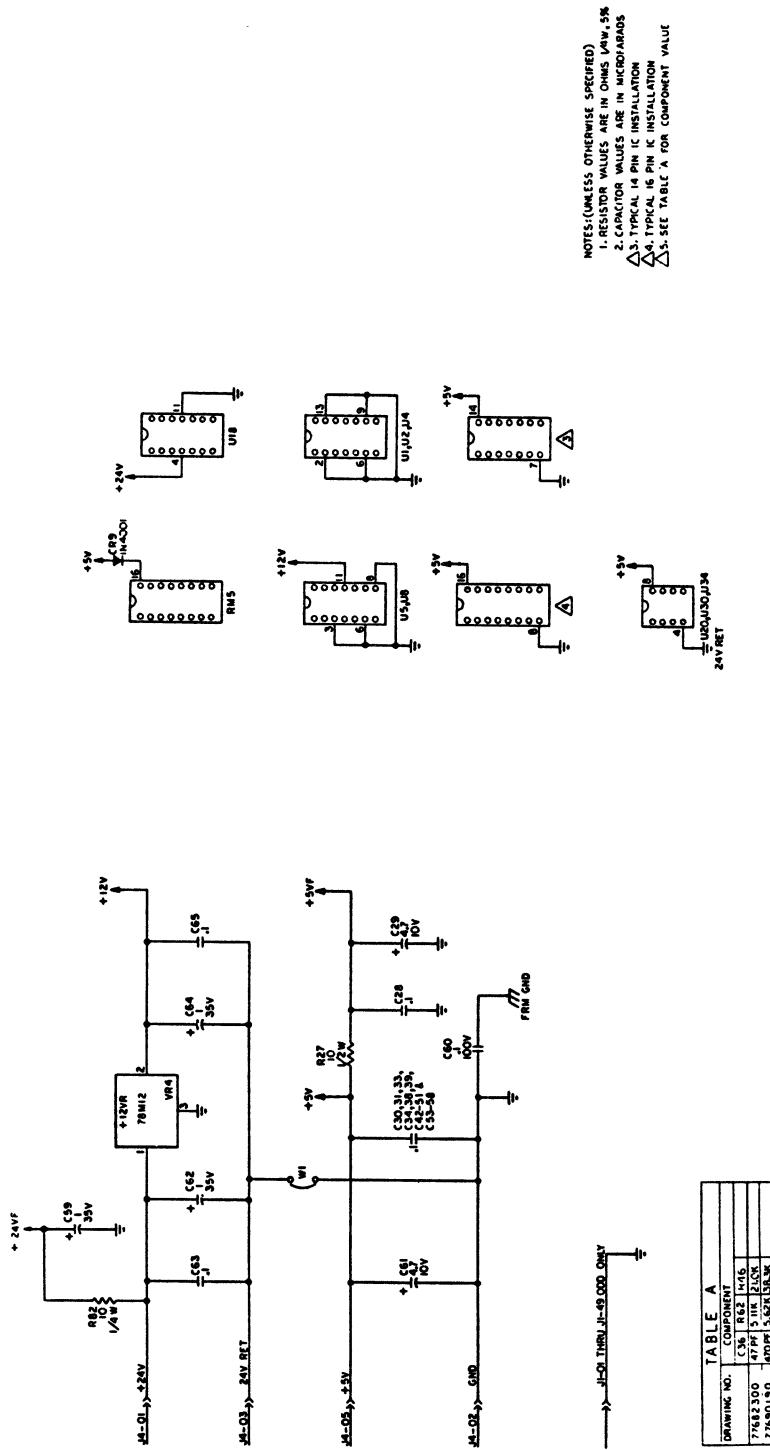

## POWER SUPPLY

The DSD 480 power supply is an open-frame unit using linear regulators. Direct current output voltages include: +5 volts, +24 volts, and unregulated -12 volts. The power supply contains two trimmer potentiometers which can be used to adjust the +5 and +24 volt outputs.

## INTERCONNECTING CABLE

The 10 foot, 26-conductor interconnecting cable serves as a signal path between the controller/formatter module and the computer interface card. The connectors on the ends of each cable are keyed on pin 23 to insure proper connection. Cable lengths greater than 10 feet require twisted pair leads and are not supplied or supported by DSD.

### **WARNING**

Interconnecting cable should never exceed 20 feet.

## CHAPTER 2

### INSTALLATION

#### UNPACKING AND INSPECTION

When your DSD 480 shipment arrives, inspect the shipping container immediately for evidence of mishandling during transit. If the container is damaged, request that the carrier's agent be present when the package is opened.

Compare the packing list attached to the shipping container with your purchase order to verify that the shipment is correct. Report any discrepancies to DSD Customer Service.

Unpack the shipping container and inspect each item for external damage such as broken controls and connectors, dented corners, bent panels, scratches and loose components.

If any damage is evident, notify DATA SYSTEMS DESIGN immediately.

Retain the shipping container and packing material for examination in the settlement of claims or for future use.

#### POWER REQUIREMENTS

The DSD 480 is shipped in one of two line voltage ranges:

100-120 VAC

or

220-240 VAC.

Systems which are configured for one range cannot easily be reconfigured for the other range.

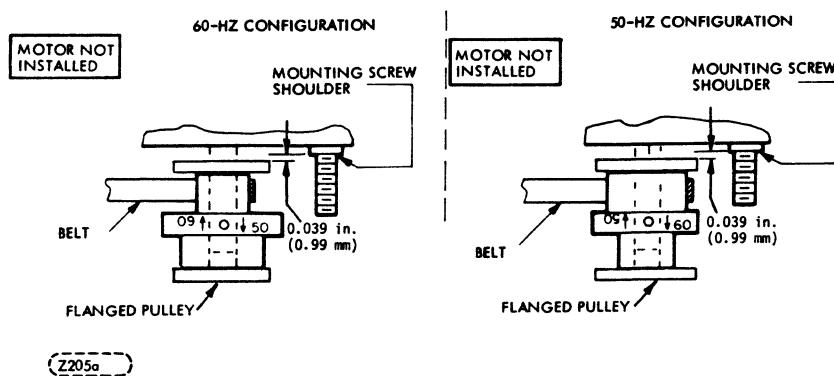

#### CAUTION

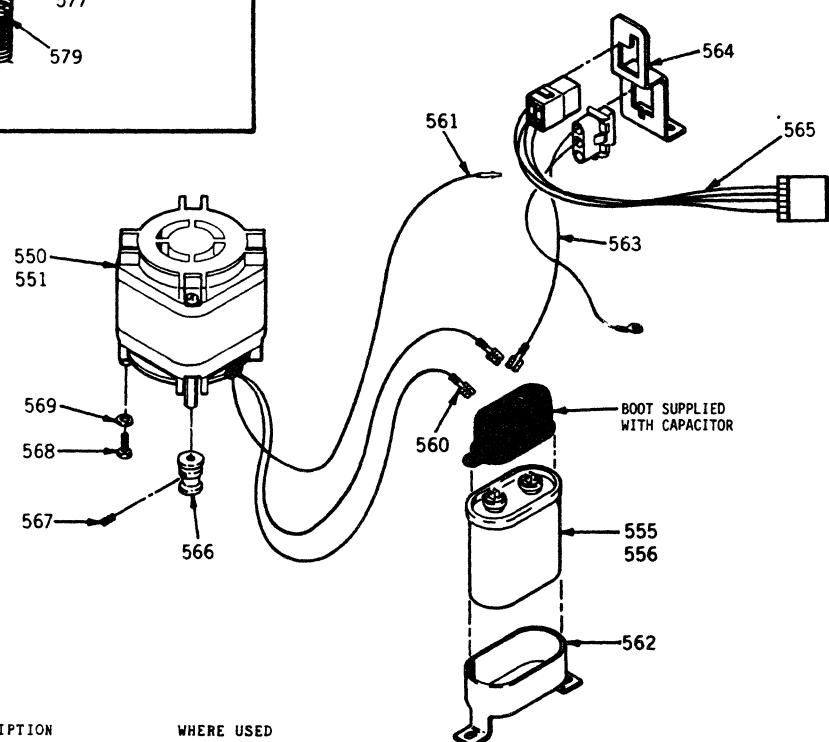

The procedure required to convert between a low voltage range (100-120 VAC) and a high voltage range (220-240 VAC) is far more complicated than just changing the position of the printed circuit board. This conversion requires changing the fan, the two AC spindle motors in the disk drives, the motor capacitors associated with the spindle motors, and the fuse. NEVER change the position of the printer circuit board from the low line voltage range (100-120 Volts) to the high voltage range (200-240 volts) without changing the AC motors. These motors will be damaged if operated at the wrong voltage.

The DSD 480 may be configured to compensate for low power line voltages (100 VAC in the low voltage range or 220 VAC in the high voltage range). If your power line voltage is below 120 VAC (or 240 VAC in high voltage range) you may reconfigure the DSD 480 to compensate as follows:

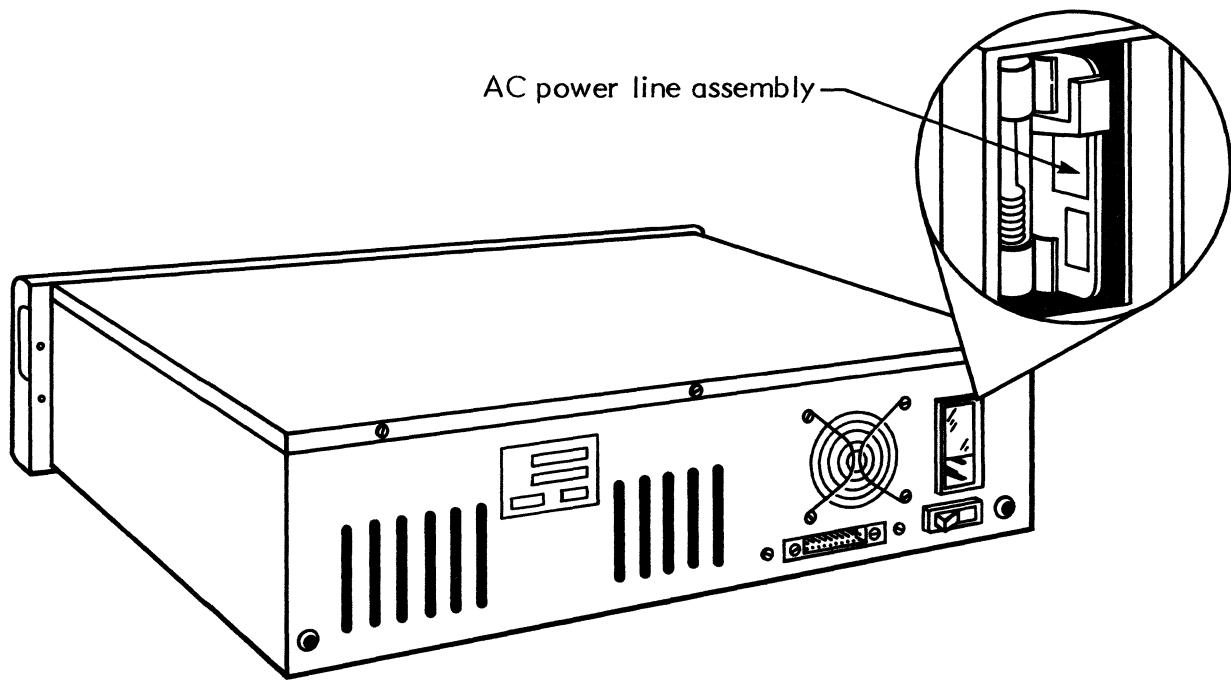

- 1) Disconnect power from the unit by removing the AC power cord from the rear of the chassis.

#### WARNING

Failure to disconnect power before attempting this procedure may cause bodily injury.

- 2) Slide plastic shield to expose fuse.

- 3) Remove fuse by moving the lever marked "FUSE PULL".

- 4) Remove PC board adjacent to fuse holder. (See Figure 2-1)

- 5) Reorient and replace PC board so that desired voltage marking is visible after installation.

- 6) Replace fuse and reattach power card.

Figure 2-1. AC Power Connector Assembly

The DSD 480 is shipped in either a 60 Hz or a 50 Hz configuration. The line frequency must be within 1 Hz of the proper value for correct operation.

## OPERATIONAL ENVIRONMENT

All flexible disk systems manufactured by DATA SYSTEMS DESIGN perform efficiently in normal computer room environments. Temperature, humidity, and cleanliness are three environmental considerations that can affect the reliability of diskette use. Refer to the DSD 480 data sheet for system specifications.

## INSTALLING THE DSD 480 CHASSIS

The DSD 480 chassis must be installed within ten feet (3 meters) of the interface module's location to accommodate the length of the interconnecting cable. If the computer system operator will be changing diskettes often, it may be convenient to install the chassis close to the console terminal.

The DSD 480 may be either mounted in a standard 19-inch rack or installed on a table top.

The DSD 480 chassis should be mounted in such a way that the air flow behind the fan is unrestricted. The temperature of the air entering the chassis should not exceed 40°C (104°F).

The following procedure should be used to mount the DSD 480 in a standard 19 inch instrumentation rack:

### NOTE

The DSD 480 is shipped in Mode 2 (RX02 compatible configuration. If you wish to change this configuration, or to run the HYPERDIAGNOSTIC exercisers for incoming inspection, it will be easier to do so before installing the unit in a rack. To change the operating mode, refer to the "HARDWARE MODES" section of Chapter 2. The HYPERDIAGNOSTICS are described in detail in Chapter 5.

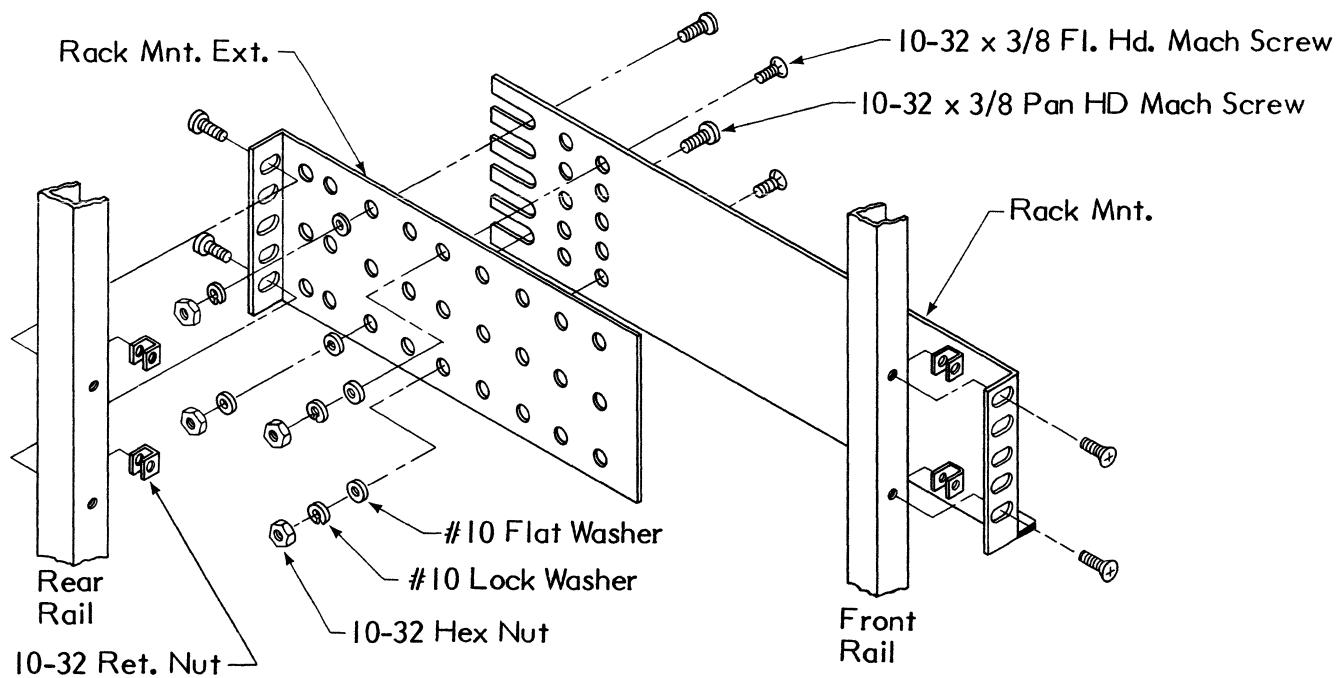

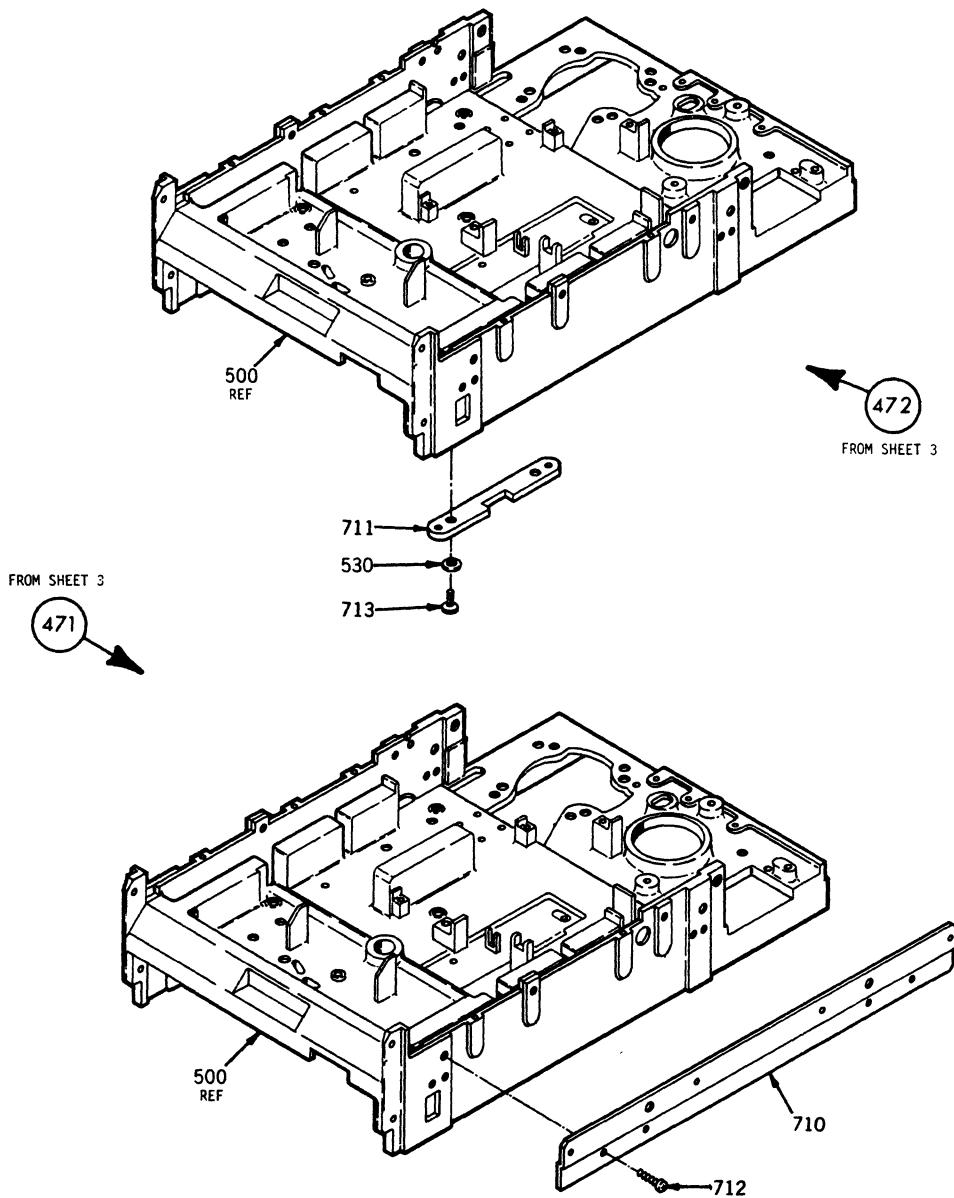

- 1) Attach the optional slim-line chassis mounts to your rack using the hardware supplied with the mounts. Note that the left and right rear extender brackets are not interchangeable. Figure 2-2 illustrates the correct relationship of the rack mounting components.

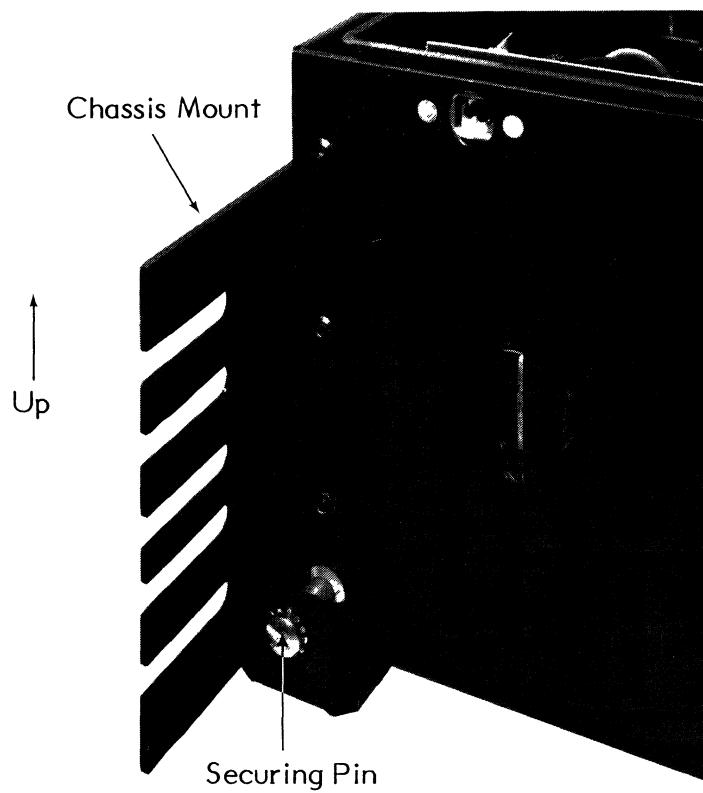

- 2) Slide the DSD 480 chassis on the mounts until the two bullets at the rear of the chassis mounts engage the corresponding holes in the rear of the chassis as shown in Figure 2-3.

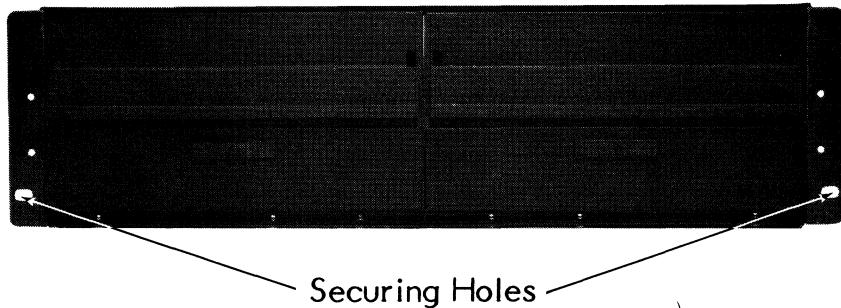

- 3) Remove the molded front "pop" panel from the chassis by pulling out the top of the panel.

DSD P/N 700025-01

Figure 2-2. Chassis Slides Mounting

- 4) Secure the chassis in the rack by bolting the front flange to the front rails of the rack as shown in Figure 2-4.

Figure 2-3. Securing the DSD 480 in a Rack

Figure 2-4. Front View of Chassis with Front Panel Removed to Show Securing Holes

You may now replace the "pop" panel by pushing it straight back onto the two "head locks".

#### DSD 480 CHASSIS CABLE CONNECTIONS

The following procedure describes the installation of the AC power cord and the interface bus cable:

- 1) VERIFY LINE POWER SWITCH IS OFF.

- 2) Plug the female end of the power cord into the connector on the back of the chassis. (The plastic shield must be raised.)

- 3) Plug the other end into an AC power receptacle.

- 4) Route the free end of the interface bus cable over to the rear of the chassis.

- 5) Plug the interface cable into the 26 pin connector so that the striped side of the cable is toward the middle of the chassis.

Be sure the position of the clipped pin in the chassis connector matches the position of the plugged hold in the cable connector.

#### INSTALLING THE DSD 480 INTERFACE MODULE AND CABLE

Ensure that all system and line power is off before proceeding with this section of the DSD 480 installation. There are separate procedures for LSI-11 and PDP-11 based systems.

The hardware bootstrap program on the interfaces is preset to a specified range of addresses. These addresses may conflict with other devices or bootstraps already installed in your computer. In order to resolve address conflicts, you may either

disable the bootstrap completely or move it to an alternate base address. We recommend that the bootstrap be moved rather than disabled in order to keep it available.

### LSI-11 Based Systems

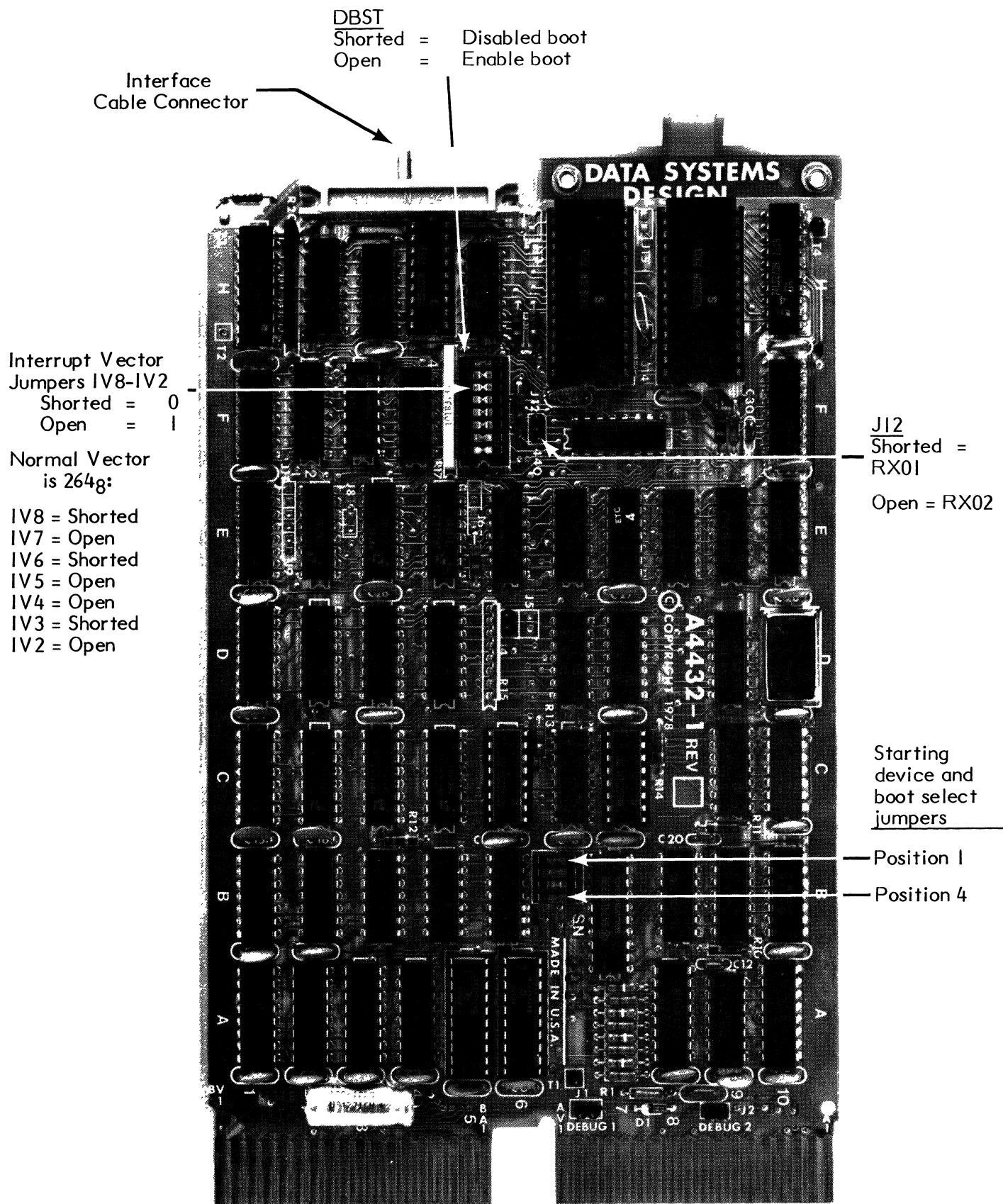

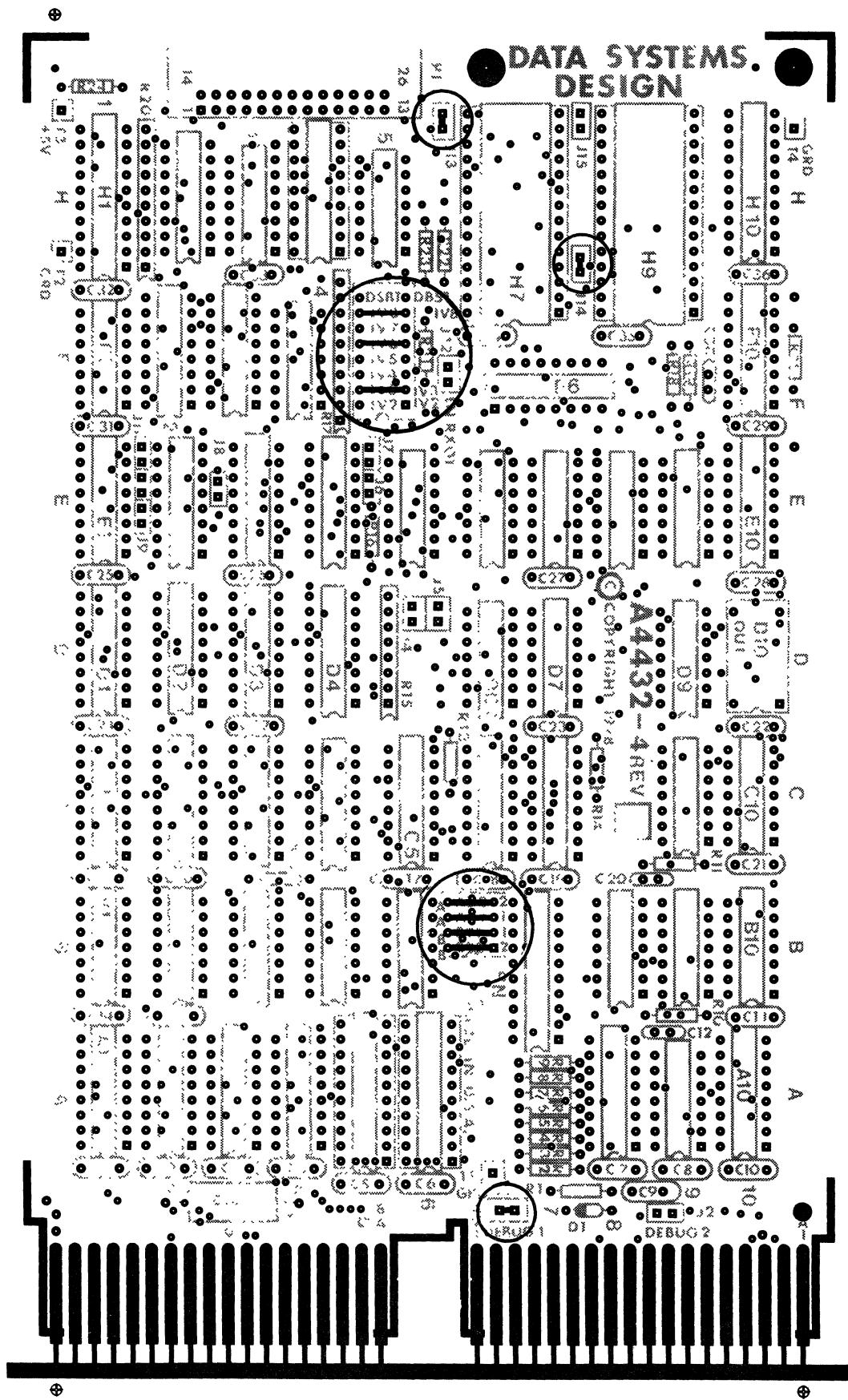

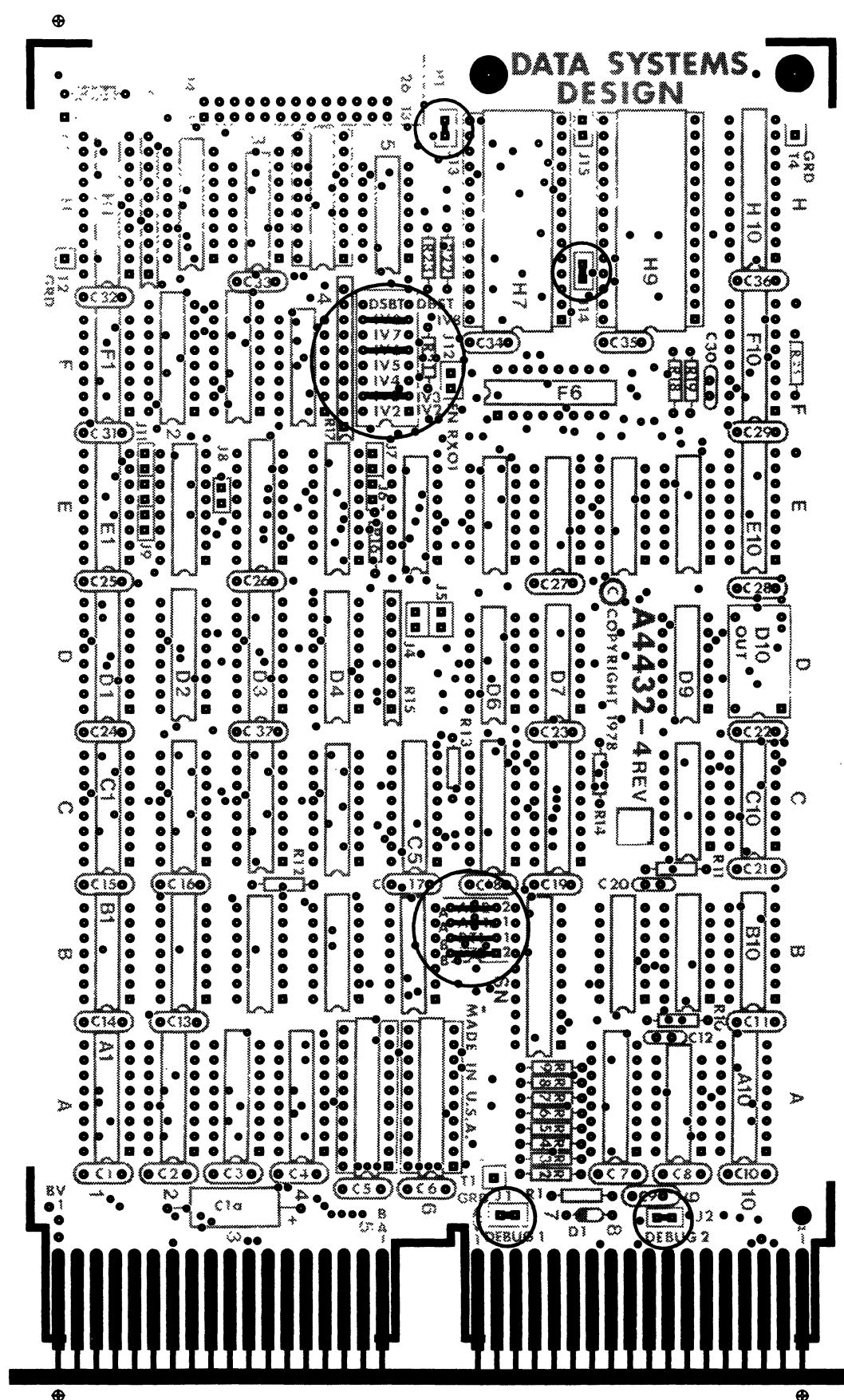

The DSD 480 interface module for LSI-11 based systems, including the PDP-11/03, is a dual-wide card marked "P/N 4432". DATA SYSTEMS DESIGN ships this interface module configured as follows:

|                     |                          |

|---------------------|--------------------------|

| REGISTER ADDRESS:   | 777170                   |

| BOOTSTRAP PROM:     | ENABLED AT 773000        |

| INTERRUPT VECTOR:   | 264                      |

| INTERRUPT PRIORITY: | BR4                      |

| OPERATING MODE:     | MODE 2 (RX02 COMPATIBLE) |

The module allows you to select one of four device register addresses, one of four bootstrap PROM (Programmable Read Only Memory) starting addresses, and a 7-bit interrupt vector address. Table 2-1 lists standard and alternate addresses for the registers and starting boot PROMs. As shown in Figure 2-5, there is a separate jumper which, when installed, disables the bootstrap PROM.

Table 2-1. LSI-11 Register and Boot PROM Addresses

| STARTING REGISTER ADDRESS  | POSITION 1 | POSITION 2 |

|----------------------------|------------|------------|

| 777170 (STANDARD)          | CLOSED     | CLOSED     |

| 777160                     | OPEN       | CLOSED     |

| 777140                     | CLOSED     | OPEN       |

| 777150                     | OPEN       | OPEN       |

| STARTING BOOT PROM ADDRESS | POSITION 3 | POSITION 4 |

| 773000 (STARTING)          | CLOSED     | CLOSED     |

| 771000                     | OPEN       | CLOSED     |

| * 775000                   | CLOSED     | OPEN       |

| ** 766000                  | OPEN       | OPEN       |

\* Use only this address of the system if configured for 31K of memory (0-774000).

\*\* Do not use this address for the bootstrap in systems with over 28K of memory.

### NOTE

When the interrupt vector jumpers are in place, the associated bit of the vector address is a "0". Thus, if all seven vector jumpers were to be installed, the vector address would be 000. Check your module against Table 2-1 and Figure 2-5 to ensure that it has been configured to match your system requirements before installation. Most system software assumes a device address of 777170 and an interrupt vector of 264. If

Figure 2-5. LSI-11 Computer Interface Card Diagram

you change either of these numbers, corresponding changes will be required in the software. Also, be sure to read the explanation of the bootstrap and diagnostic programs if non-standard addresses are used.

The following procedure describes how to install the LSI-11 interface module:

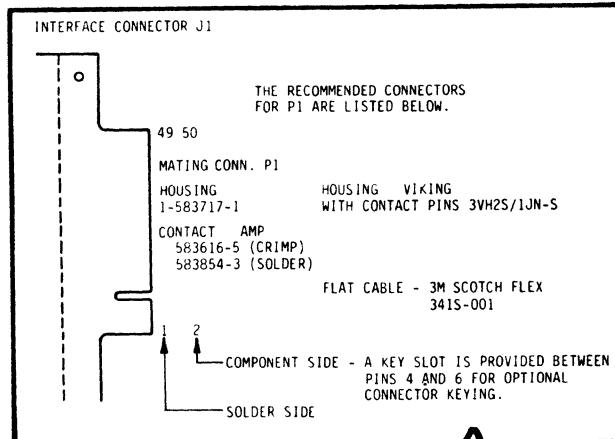

- 1) VERIFY LINE POWER IS OFF

- 2) Plug one end of the interface cable into the interface module so that pin 1 (the striped side) is closest to the edge of the board. Note that the position of the clipped pin on the module connector matches the position of the plugged hole on the cable connector.

- 3) Plug the opposite end of the interface cable into the keyed connector mounted on the rear panel of the chassis. Note that the position of the clipped pin on the module connector matches the position of the plugged hole on the cable connector.

Now you are ready to plug the module into the lowest numbered available Q-Bus slot.

#### NOTE

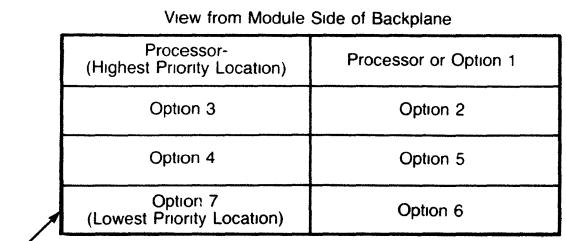

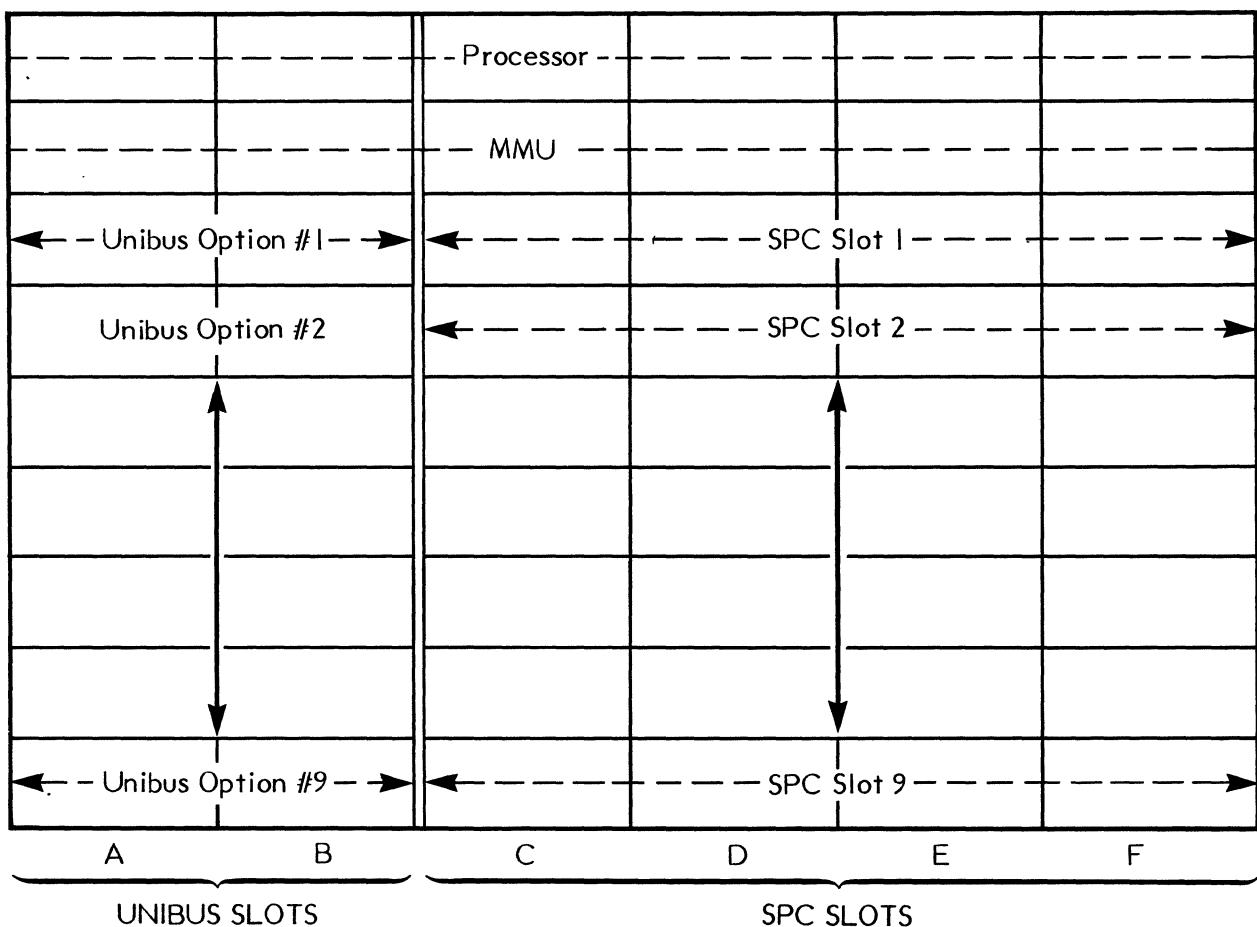

No open Q-Bus slots are allowed between the processor and the DSD 4432 interface module. Since this module uses both interrupts and DMA (Direct Memory Access), a break in either of the grant propagation chains will prevent the interface module from obtaining control of the Q-Bus. Figure 2-6 shows how Q-Bus slots are numbered on the standard backplanes available from DEC. Some Q-Bus interface cards (e.g. serial interfaces and memory) do not pass the DMA grant signal. Ensure that the DMA signal is reaching the LSI-11 interface (4432).

#### PDP-11 BASED SYSTEMS

The DSD 480 interface module for all PDP-11 based systems, except the PDP-11/03, is a quad card. DATA SYSTEMS DESIGN ships this interface module configured as follows:

|                     |                          |

|---------------------|--------------------------|

| REGISTER ADDRESS:   | 77170                    |

| BOOTSTRAP PROM:     | ENABLED AT 771000        |

| INTERRUPT VECTOR:   | 264                      |

| INTERRUPT PRIORITY: | BR5                      |

| OPERATING MODE:     | MODE 2 (RX02 COMPATIBLE) |

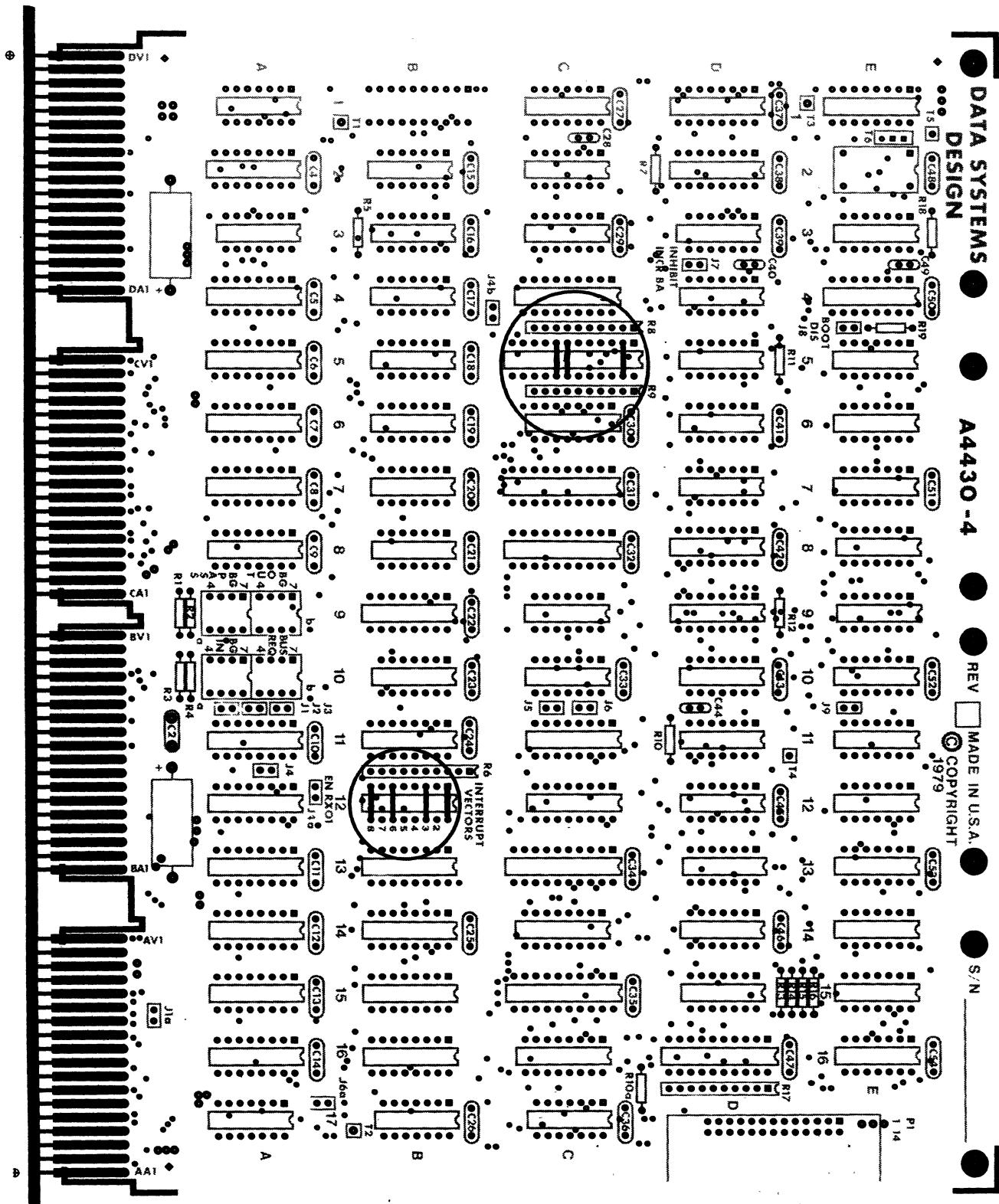

This interface module is marked "4430".

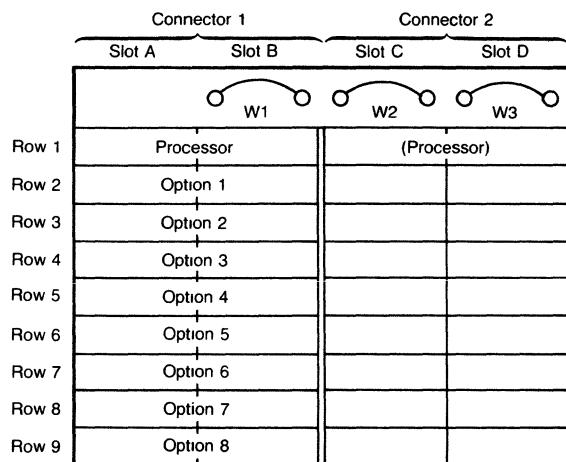

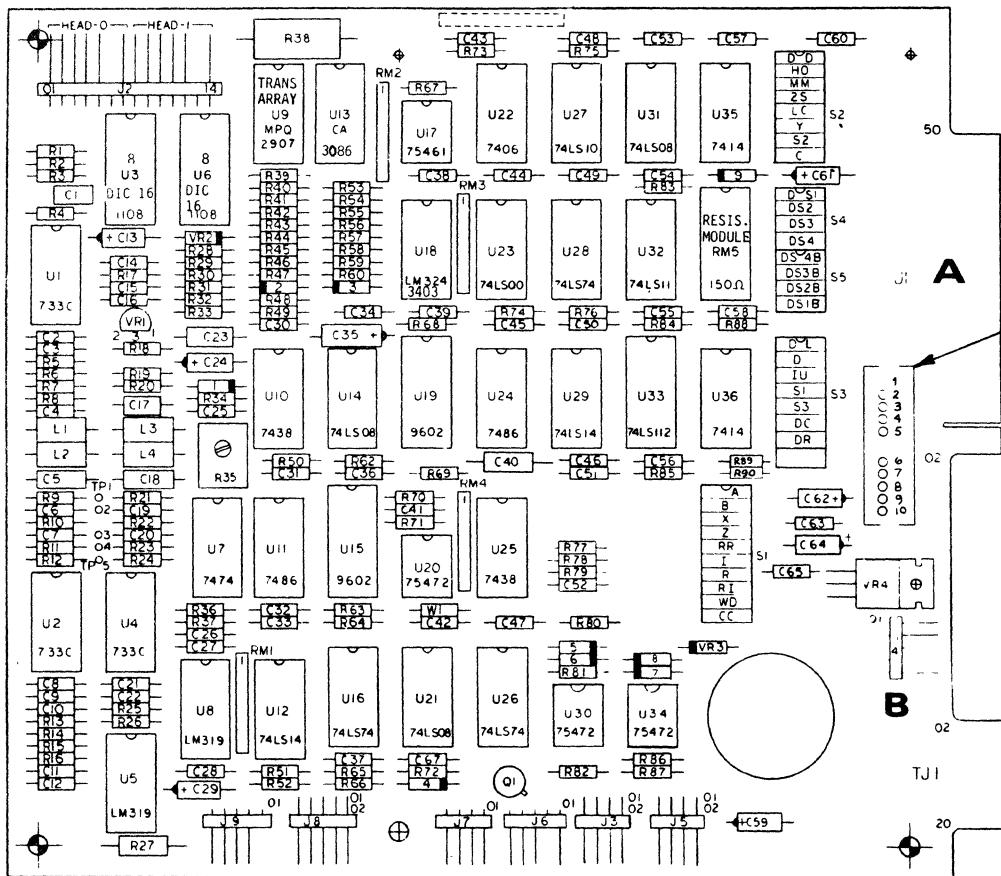

The twelve position shunt located at coordinates C-5 on the 4430 interface module is used to configure device register addresses and the bootstrap program starting address. Figure 2-7 is an illustration of the PDP-11 interface module. It shows how the twelve shunt positions are numbered.

## DEC Backplane H9270

View is from Module Side of Connectors.

## DEC Backplane H9273-A

## DEC Backplane DDV 11-8

Figure 2-6. Option Priority in LSI-11 Backplanes

Twelve position shunt used for

selecting bootstrap address and

device register address

Bootstrap

Disable

Jumper

Eight position

Interrupt Vector Shunt

Figure 2-7. PDP-11 Computer Interface Card Diagram

Shunt positions 1 and 2 are used to configure the bootstrap program starting address as follows:

| <u>STARTING BOOT PROM ADDRESS</u> | <u>POSITION 1</u> | <u>POSITION 2</u> |

|-----------------------------------|-------------------|-------------------|

| 773000                            | OPEN              | OPEN              |

| 771000 (STANDARD)                 | OPEN              | CLOSED            |

| 775000                            | CLOSED            | OPEN              |

| 766000                            | CLOSED            | CLOSED            |

The bootstrap program contained on the interface module occupies 256 words of memory space, starting at one of the four selectable addresses shown above. If you do not want the bootstrap program to respond to any addresses, the bootstrap disable jumper should be installed as shown in Figure 2-7.

Shunt positions 3 through 12 correspond to address bits A3 through A12 respectively when configuring the device register address. A closed shunt position corresponds to a binary 0 and an open shunt position corresponds to a binary 1. When the PDP-11 interface module is shipped, it is configured to respond to a base register address of 777170 (octal). This is done by having shunt positions 7 and 8 left closed, and positions 3, 4, 5, 6, 9, 10, 11 and 12 punched open.

The eight position shunt located at coordinates B-12 is used to configure the interrupt vector address. Figure 2-7 shows how the eight shunt positions are numbered. Position 1 is not used. Positions 2 through 8 correspond to interrupt vector address bits IV2 through IV8 respectively. A closed shunt position corresponds to a binary 0 and an open shunt position corresponds to a binary 1.

When this interface module is shipped, it is configured to have an interrupt vector address of 264 (octal). This is done by having shunt positions 3, 6 and 8 left closed, and positions 2, 4, 5 and 7 punched open.

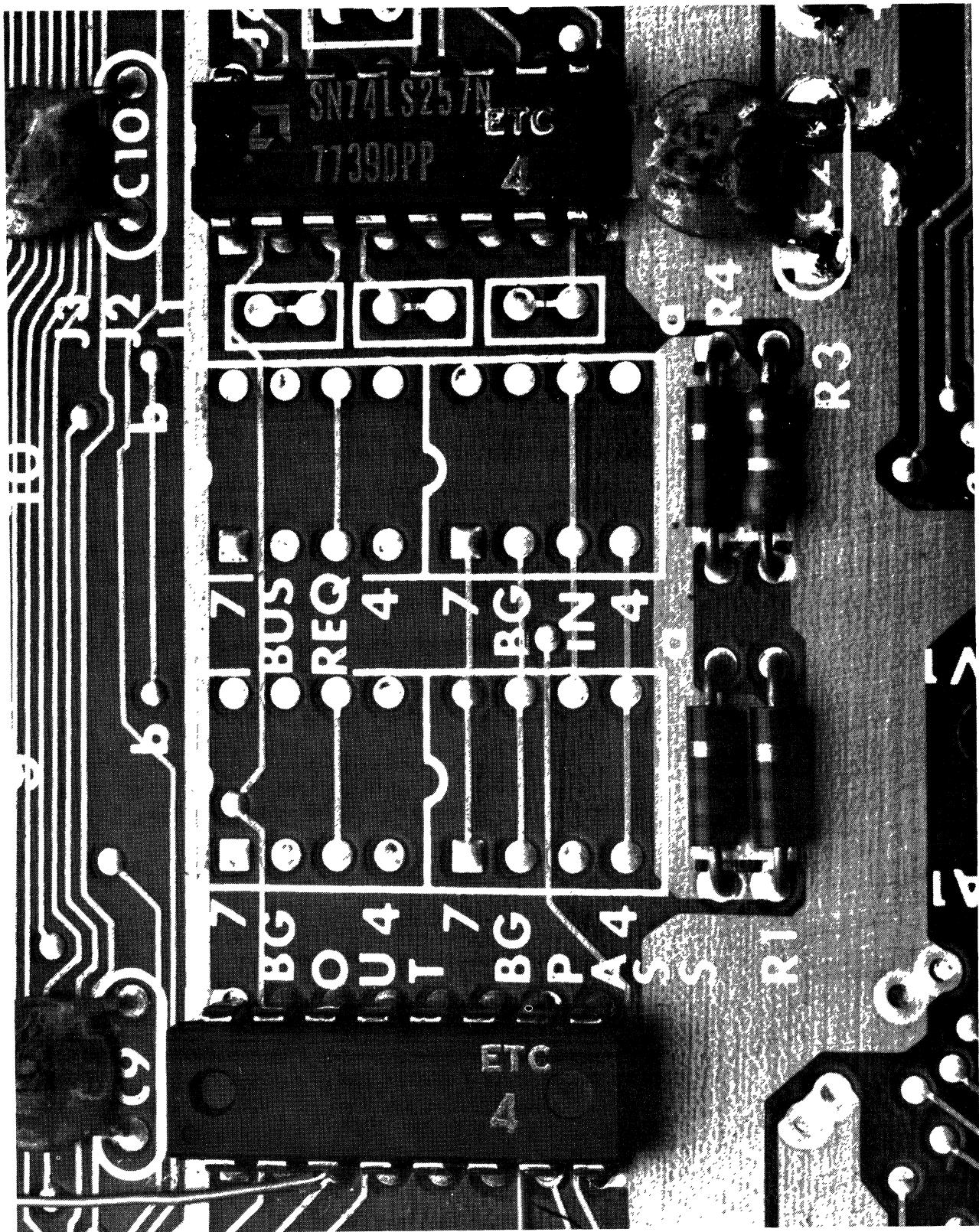

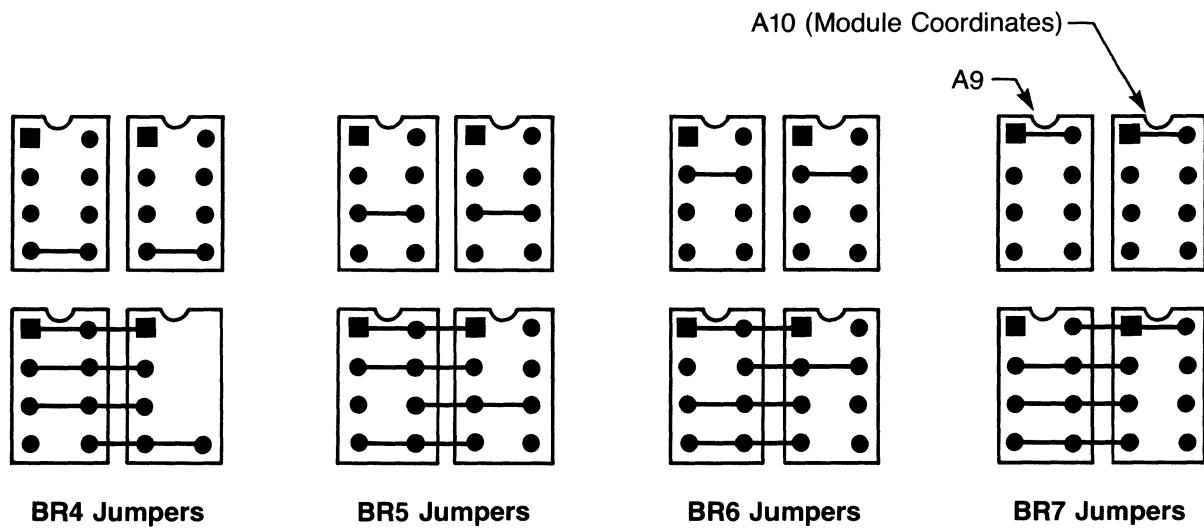

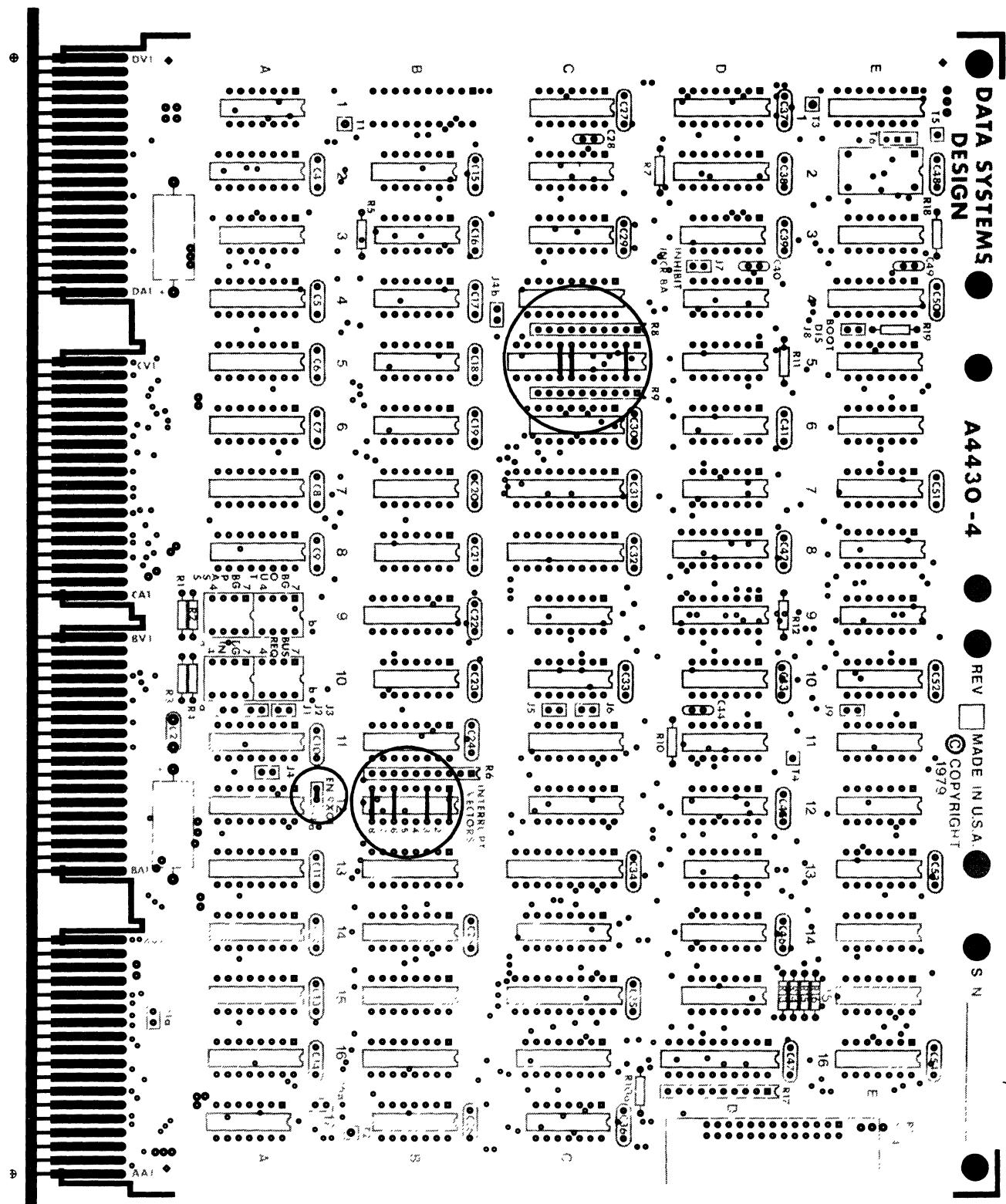

If the interrupt priority level must be changed, cut and jumper the circuit board to resemble the diagram corresponding to the desired interrupt priority level as shown in Figures 2-8 and 2-9. If the priority levels will be changed often, cut the six permanent traces and install the four 8-pin IC sockets in the positions outlined on the board. Placing either four-position shunts or DIP-Switches in the sockets will allow for repeated jumper changes. The interrupt priority jumpers are located at coordinates A-9 and A-10 on the interface module circuit board. Interrupt priority level 4 is the lowest and level 7 is the highest.

If the system is to be operated in Mode 1 (RX01 compatible) when the EN RX01 jumper located near coordinates A-12 must be installed. This number is removed for RX02 compatible operation.

Figure 2-8. PDP-11 Interrupt Priority Levels

Figure 2-9. PDP-11 Interrupt Priority Jumper Diagram

The following procedure describes how to install the PDP-11 module:

- 1) **VERIFY LINE POWER IS OFF.**

- 2) Check that the jumpers on the interface module are configured correctly.

- 3) Plug one end of the interface cable into the interface module so that pin 1 (striped side) is closest to the module handle.

- 4) Confirm that the position of the clipped pin on the module connector matches the position of the plugged hole on the cable connector.

- 5) Plug the module into a convenient SPC (Small Peripheral Controller) slot.

Be sure there is grant continuity between the processor and the interface module. If there are open SPC slots between the processor and the interface module, place a grant continuity card in slot D.

## NOTE

Since the 4430 interface module uses DMA (Direct Memory Access), you must be sure there is no backplane jumper or foil trace between backplane pins CA1 and CB1 of the selected SPC slot. These two pins normally connect NPG (Non-Processor Grant) IN to NPG OUT. Usually the pins are left connected since most Small Peripheral Controllers do not use DMA. If this jumper is not removed and a 4430 interface module is installed configured either for RX01 or RX02 compatible operation, the computer system will stop. Replace the jumper any time the 4430 module is removed.

FRONT

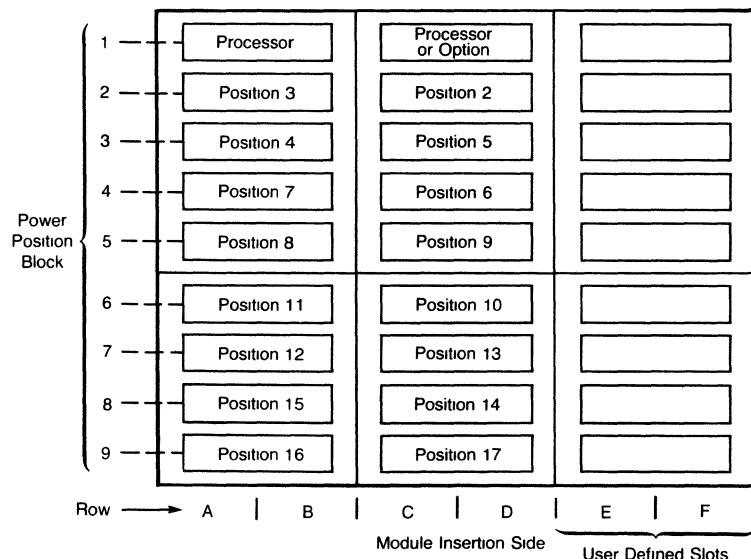

Figure 2-10. Typical UNIBUS Hex Backplane

## HARDWARE MODES

The DSD 480 may be configured for one of three operating modes or a "HYPERDIAGNOSTIC" mode. The desired mode is selected by means of a DIP-Switch located on the controller module. Each mode is described briefly below and in detail in Chapters 4 and 5. The DSD 480 is shipped in Mode 2 (RX02 compatible).

### Mode 1 (RX01 Compatible)

In RX01 mode, the DSD 480 emulates the DEC RX01. Recording is done in IBM 3740 (DEC single density) format only. Data are transferred by programmed I/O. Single sided diskettes only may be used in RX01 mode.

### Mode 2 (RX02 Compatible)

In the RX02 mode, the DSD 480 is configured to emulate the DEC RX02. In this mode, it reads and writes in DEC double density and IBM 3740 single density diskette formats. Data are transferred by DMA. The DSD 480 also reads and writes on double-sided diskettes in DEC double density, IBM 3740 (DEC single density) and IBM 2D-256 double density formats. The DSD RT-11 monitor patch program must be executed to activate two-sided operation under RT-11. The procedure is described in Chapter 4. Once this operation has been performed, these formats are transparent to DEC software.

### Mode 3 (Extended IBM)

The DSD 480 IBM mode is a "superset" of the RX02 mode. In addition to the RX02 mode formats, the DSD 480 also reads and writes in all other IBM formats. A modified software handler is required to support the additional formats not available in Mode 2 (RX02). More detail is provided in the software section, Chapter 4.

### "HYPERDIAGNOSTIC" Mode

DSD's exclusive "Hyperdiagnostics" are a library of microprogrammed routines for stand-alone exercising and monitoring of the disk system. The routines are selected from the DIP-Switch or the controller module. Chapter 5 provides a complete description of "Hyperdiagnostic" operation.

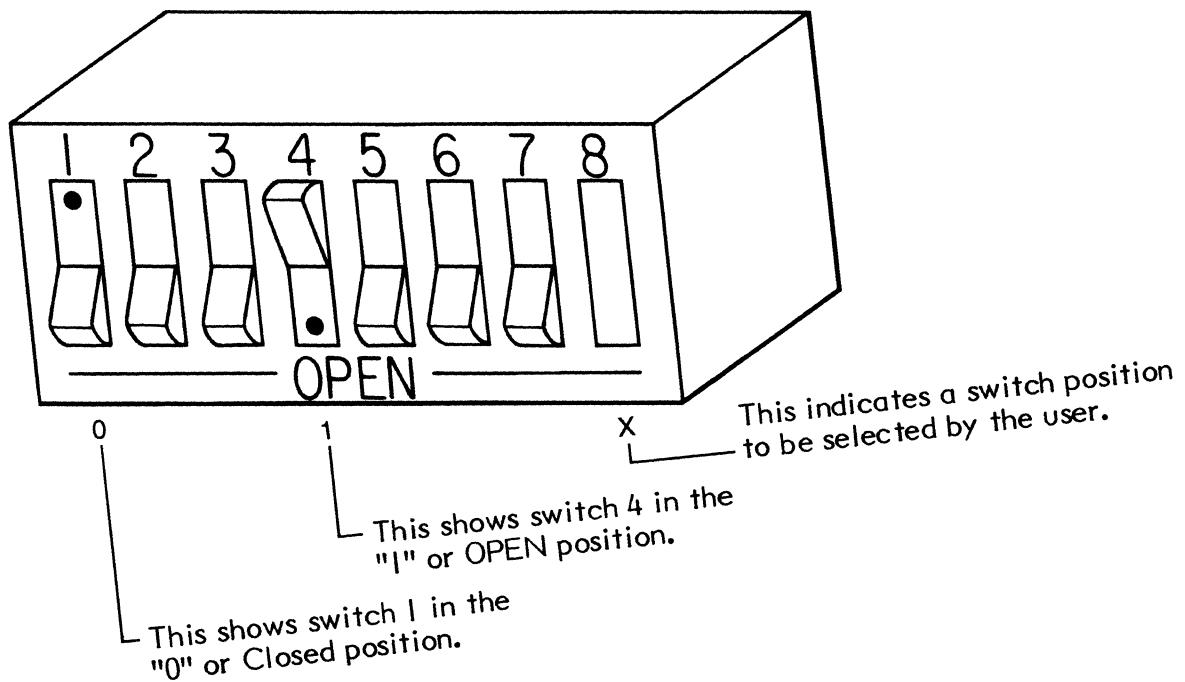

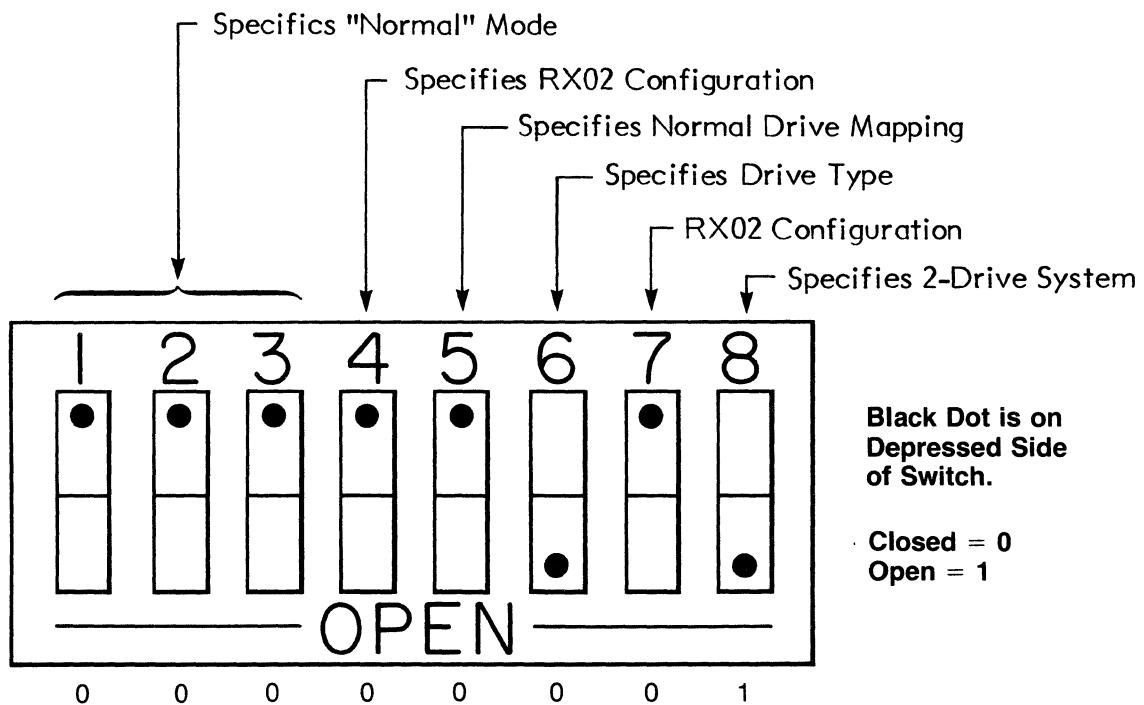

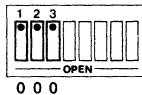

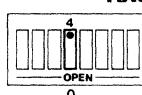

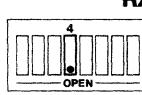

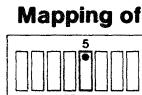

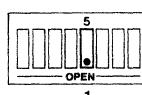

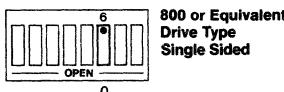

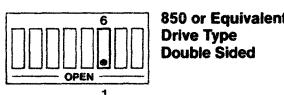

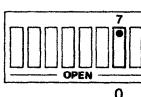

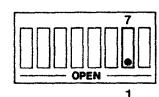

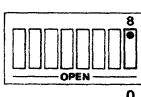

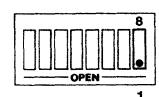

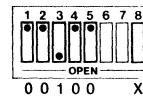

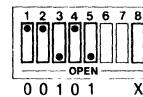

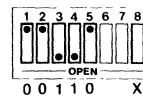

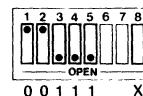

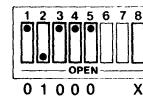

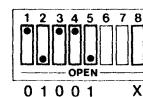

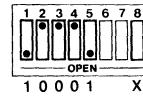

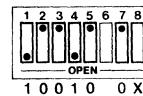

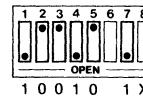

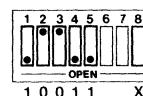

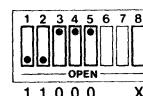

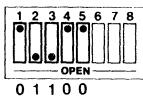

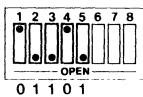

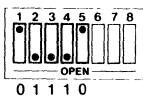

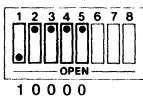

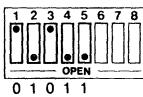

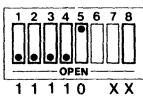

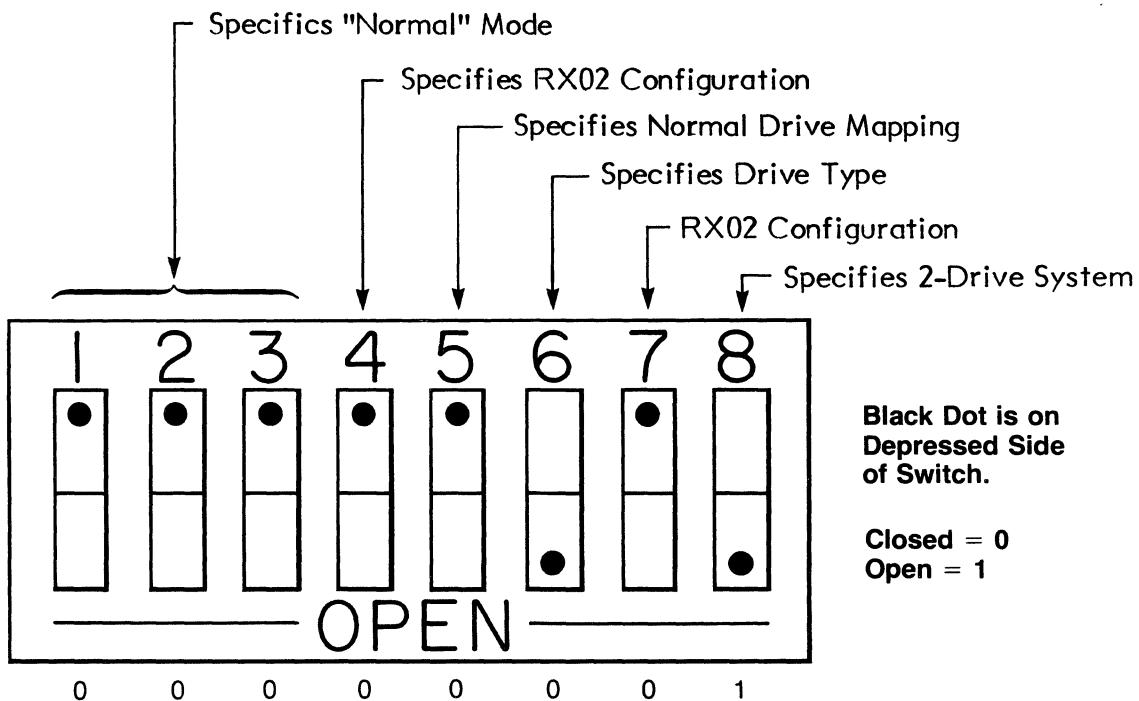

### Switch Selection of Operating Mode

DATA SYSTEMS DESIGN ships the DSD 480 configured for Mode 2 (RX02 Compatible) operation. Selection of other modes is done via the DIP-Switch on the controller module. For Mode 1 operation, the jumper "ENRX01" on the LSI-11 or PDP-11 interface card must also be installed. Figure 2-11 shows the DIP-Switch selector. The switches may be set conveniently with a ball point pen or other sharp implement. Table 2-2 lists the controller DIP-switch functions. Figure 2-12 illustrates the proper switch settings for normal mode operation.

Figure 2-11. Controller/Formatter Module DIP-Switch

Table 2-2. Controller and DIP-Switch Functions

| SWITCH NUMBER | SWITCH NAME             | WHEN CLOSED                                                         | WHEN OPEN                                   |

|---------------|-------------------------|---------------------------------------------------------------------|---------------------------------------------|

| 1,2,3         | Self Test Select        | All Closed for Normal Operation                                     | Selects a Hyper Diagnostic Function         |

| 4             | Mode Select             | Selects RX02 or Mode 2 (RX02 compatible) or Mode 3 (IBM compatible) | Select Mode 1 (RX01 compatible)             |

| 5             | Drive Mapping Select    | Left Drive = Unit 0<br>Right Drive = Unit 1                         | Right Drive = Unit 0<br>Left Drive = Unit 1 |

| 6             | Drive Type Select       | Single Sided Drive                                                  | Double Sided Drive                          |

| 7             | Extended Format Select  | Mode 2<br>Read all DEC and IBM 26 Sector Formats                    | Mode 3<br>Read all DEC and IBM Formats      |

| 8             | Select Number of Drives | Operate One Drive                                                   | Operate Two Drives                          |

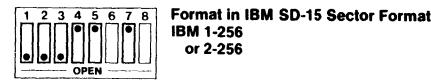

Figure 2-12. Controller DIP-Switch Settings: Normal Modes

## CHAPTER 3

### BASIC SYSTEM OPERATION

This section explains how to turn on and operate your DSD 480 after correctly installing it. Chapter 2 details the installation procedure.

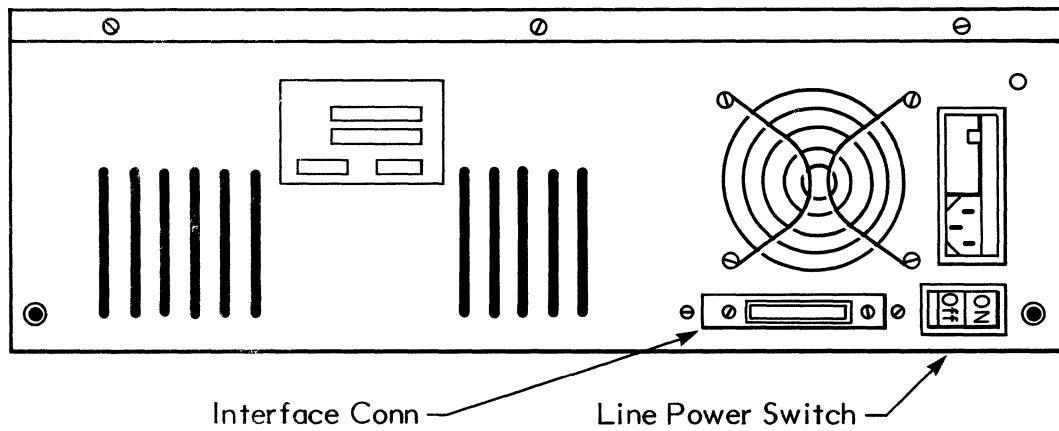

#### APPLYING AC POWER

Once the correct AC (alternating current) power is connected, simply turn the line switch on the DSD 480 chassis to the "ON" position. The location of the line switch is shown in Figure 3-1.

The DSD 480 chassis and the interface module can be safely powered up in either order. There is no danger of writing on diskettes loaded in the drives during power up or power down cycles.

Figure 3-1. Back Panel of DSD 480

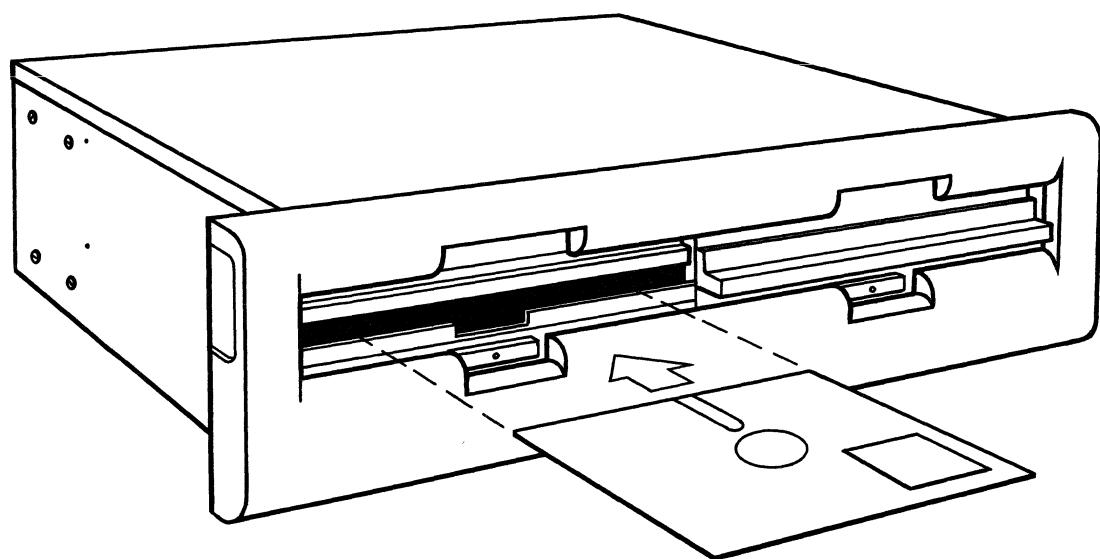

## INSERTING A DISKETTE

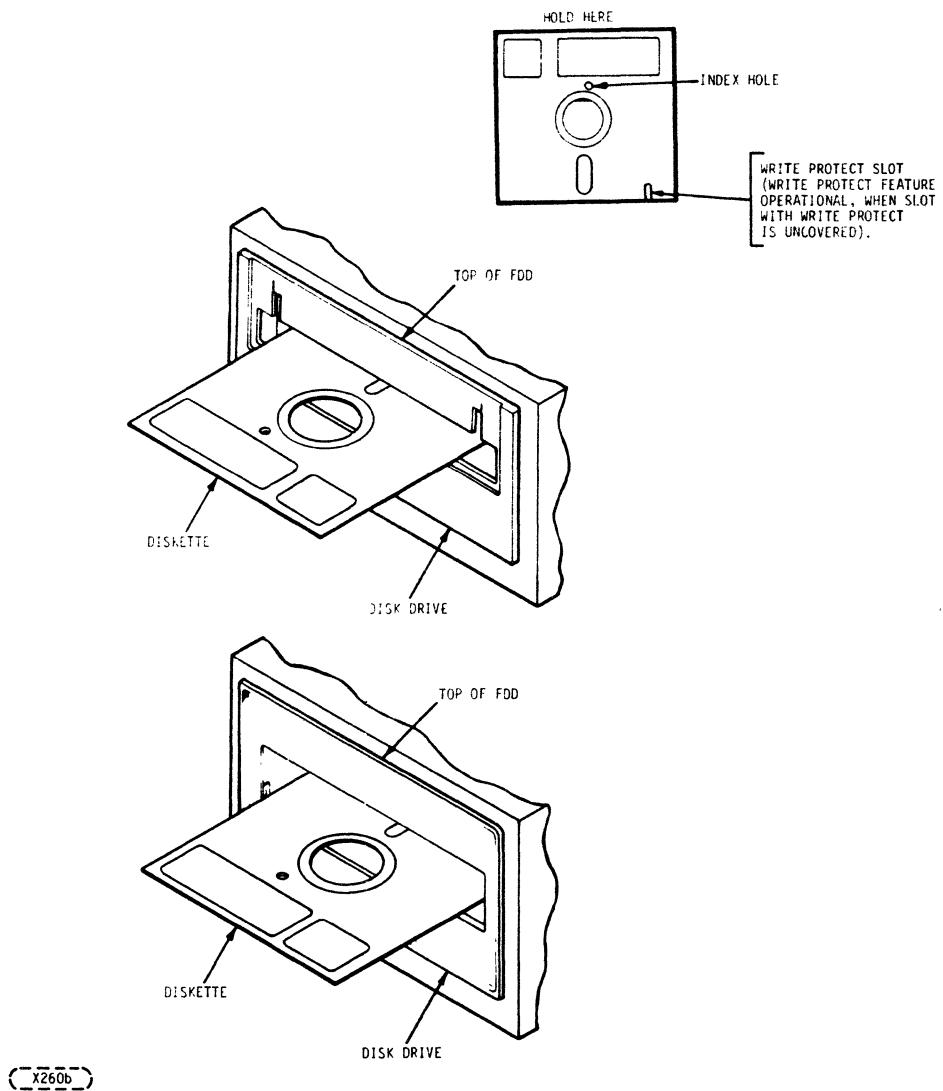

Open the DSD 480 drive door, and insert the diskette into the drive as shown in Figure 3-2. Close the drive door.

You are now ready for an initialization response check of your computer and flexible disk system.

Figure 3-2. Orientation of Diskette for Insertion

## INITIALIZATION RESPONSE CHECK

When the DSD 480 is connected correctly to the host computer, it performs an initialization response (INIT) upon power-up. An initialization response can also be forced by any of the following operator console actions:

### LSI-11 BASED SYSTEMS

- 1) Flip the INIT switch (if there is one) on the host computer.

- 2) Using ODT (Octal Debugging Tool), enter the "G" command at any arbitrary starting address.

- 3) Using ODT, write the number 40000 into the DSD 480 RXCS register, normally at address 777170.

### PDP-11 BASED SYSTEMS

- 1) Generate a UNIBUS INIT by depressing the START switch or button on the processor.

- 2) Using the console, write the number 40000 into the DSD 480 RXCS register, normally at address 777170.

Each time you generate an INIT, you should hear the drives as the controller moves the head to track 0. The activity lights on the front of the drives should come on briefly. If a diskette is loaded into drive 0 (normally the left hand drive) you should also hear the head load. The drive 0 activity light remains on slightly longer as the controller reads track 1/sector 1 of the diskette into the sector buffer.

If you did not observe the results described above, ensure that you have:

- 1) Applied power to both the computer mainframe and the DSD 480 chassis.

- 2) Connected both ends of the DSD 480 interface bus cable in the proper orientation. (The red drive select lights remain on if the cable is reversed.)

- 3) Generated a system or device initialize signal by one of the methods described above, and the signal is reaching the DSD 480 interface.

- 4) Closed the drive doors.

- 5) Set the controller module DIP-Switch as described earlier in this chapter.

- 6) If the system fails to respond, the problem may be caused by low power supply voltage. This condition is indicated if all LEDs on the 480 controller board (inside chassis) are illuminated.

If you are still unable to force an INIT, refer to Chapter 5.

## SYSTEM BOOTSTRAPPING

### STANDARD LSI-11 AND PDP-11 SYSTEMS

Before attempting to bootstrap your DEC operating system diskette, ensure that the DSD 480 operating mode (RX01 or RX02 compatible) matches the system device handler. The DSD 480 will boot from either single or double sided DEC-formatted diskettes if the appropriate operating system files are present. Mode 1 (RX01 compatible) operates with single sided, single density diskettes only. The RT-11 monitor files DXMNSJ.SYS or DXMNFB.SYS must be present.

In Modes 2 and 3, the DSD 480 will boot from either single or double density diskettes provided that the file DYMNSJ.SYS or DYMNFB.SYS is present. Chapter 4 describes how to convert a single density operating system diskette to double density operation. It also describes how to generate bootable double-sided diskettes.

#### NOTE

For 2-sided diskettes the monitor files must be on side zero.

The DSD 480 features a built-in hardware bootstrap program on the LSI-11 and PDP-11 interface modules. When this 512-byte (256 16 bit words) program is executed by the computer, the operating system is automatically loaded into memory from either a single or double density diskette. The bootstrap also performs diagnostics which confirm operation of the interface, controller and processor memory. These diagnostics include:

- 1) A fill and empty buffer test which verifies the sector buffer and DMA transfer capability. It loads a data pattern into the controller sector buffer, then reads it back into memory and compares the results.

- 2) A command and status register bit-latch test that confirms correct operation using the DSD 480 interface register.

- 3) A computer memory test that checks contiguous memory to 28 K for both data and address line errors.

If a malfunction is detected during execution of any of these tests, the computer either HALTs or continuously executes a program loop. If this occurs, refer to Appendix D.

### NON-STANDARD DEVICE ADDRESSES

Most DSD 480 systems are configured so the command and status register responds to address 177170. This address is regarded as the "standard" device address for the first flexible disk system installed on LSI-11 or PDP-11 based computer systems. Under certain circumstances, you may want to configure your DSD 480 system to respond to a non-standard device address. If this is done, the bootstrap procedure is slightly modified.

The following are descriptions of several types of bootstrap starting procedures:

1) RXCS at 777170

If the shunts on the interface module are set up so that the bootstrap program base address is 773000 for LSI-11 or 771000 for PDP-11, and the RXCS = 777170 (standard address), then bootstrap by starting the computer at the bootstrap program base address.

2) RXCS at 777150

If the interface module is modified so that the RXCS = 777150, the system is bootstrapped by starting the computer at the bootstrap program base address plus 20 (octal). In this case the base address is 173020.

3) Alternate Base Addresses

If the interface module is modified so that the device address is any legal address other than 777150 or 777170, follow this procedure:

- a) Write the device address (e.g. 177160) into memory address 000000.

- b) Write the number 000340 into CPU register 0 (R0).

- c) Write the number 000002 into CPU Register 1 (R1).

You can now start the computer at the bootstrap program base address plus 40 (octal). In this case the start address is 773040.

#### NOTE

If the DSD 480 is configured for a non-standard device address, the system device handler on the operating system must be altered. In addition, the bootstrap on the diskette must be updated to include the revisions to the monitor.

#### ROM (READ ONLY MEMORY) INSTALLED AS MAIN MEMORY

The DSD 480 bootstrap program reports a memory error if a block of ROM (read-only memory) is installed within the first contiguous block of read/write memory below 30 K. If you encounter a memory error caused by ROM installed as main memory, refer to the following section.

#### BOOTSTRAPPING WITHOUT SYSTEM TEST FUNCTIONS

The following procedure describes how to skip all of the system test functions included in the DSD 480 bootstrap program and to directly bootstrap the operating system:

- 1) The LINE-TIME CLOCK switch must be off.

- 2) Deposit the device address of the device to be bootstrapped in location 000000.

(typically 777170)

You may now start the CPU at 524 (octal) address locations beyond the boot base address.

#### ACCEPTANCE TESTING

When the DSD 480 is first installed, you may confirm proper operation by running the "VERIFY" routine of the software diagnostic program, FLPEXR. This routine will run continuously unless halted. All system functions will have been tested when the message "short pass completed" is printed. The diagnostic may be halted when this occurs. Please refer to Chapter 6 for a complete discussion of software diagnostics.

## CHAPTER 4

### SOFTWARE

#### OPERATING MODES

The DSD 480 has three operating modes; Mode 1 (RX01 compatible), Mode 2 (Rx02 compatible), and Mode 3 (Extended IBM). The procedure for selecting the proper mode is described in Chapter 2. Modes 1 and 2 are fully DEC-compatible. To activate double sided support in these modes, a patch to the RT-11 V3B monitor is required. The procedure is described in detail below. IBM 26 sector per track formats both single and double density can also be written or read in a DEC-compatible mode - transparent to DEC software.

In Mode 3, the DSD 480 hardware will read and write all IBM diskette formats in addition to DEC formats. A modified device software handler is required to support these formats. Mode 3 protocol is described in detail in this chapter. A complete description of the various operating modes is provided in Table 4-1.

#### DISKETTE COMPATIBILITY

The DSD 480 will accept all DEC or IBM-compatible soft-sectored diskettes. A description of the DEC and IBM formats is provided in Table 4-1.

#### NOTE

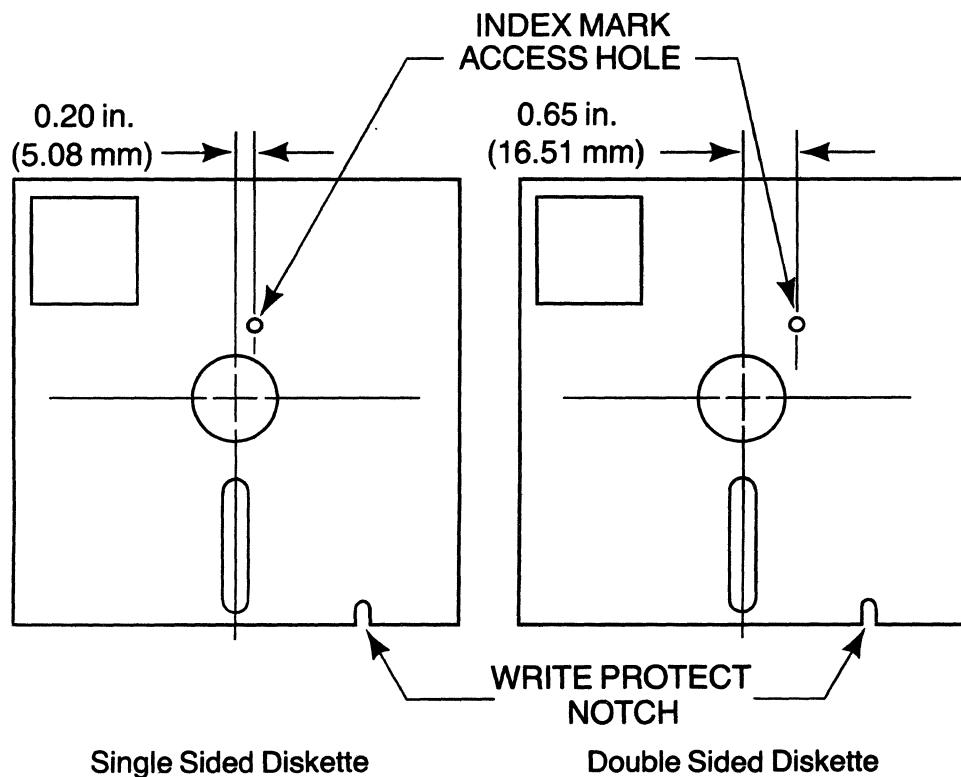

##### Single Sided Diskettes:

- 1) DEC's single sided, single density format is the same as the IBM 1-128 format (also called IBM 3740). The diskettes are equivalent and may be used interchangeably.

##### Double Sided Diskettes:

- 2) For two-sided, single density, DEC-compatible operation, the DSD 480 uses IBM 2-128 formatted diskettes. This is simply the DEC single density format repeated on both sides of the diskette.

- 3) DEC and IBM double density formats are significantly different. IBM writes both headers and data in double density while DEC writes headers in single density and data in double density. Since DEC does not currently offer double-sided diskettes, the two-sided, double density DEC format is generated from IBM 2-128 (single density) diskettes by changing the data sections to double density. Two-sided, DEC double density diskettes are easily generated on the DSD 480 using the "set media density" command described under "Formatting Diskettes."

Table 4-1. DEC and IBM Diskette Formats

| FORMAT NAME        | DISKETTE TYPE<br>(IBM PART #)                                      | FORMATTED CAPACITY<br>PER DISKETTE<br>(BYTES) | NUMBER OF SURFACES | DATA TRACKS PER SURFACE | ALTERNATE TRACKS PER SURFACE | TRACKS 1-16 | TRACK 0, SIDE 0 | TRACK 0, SIDE 1 | TRACKS 1-16 | TRACK 0, SIDE 0 | TRACK 0, SIDE 1 | BYTES PER SECTOR | SECTORS PER TRACK | IBM OR SYSTEM<br>OR DEVICE |                      |                      |                                                          |

|--------------------|--------------------------------------------------------------------|-----------------------------------------------|--------------------|-------------------------|------------------------------|-------------|-----------------|-----------------|-------------|-----------------|-----------------|------------------|-------------------|----------------------------|----------------------|----------------------|----------------------------------------------------------|

|                    |                                                                    |                                               |                    |                         |                              |             |                 |                 |             |                 |                 |                  |                   | SUPPORTED BY RX02          | SUPPORTED BY DSD 440 | SUPPORTED BY DSD 470 | SUPPORTED BY DSD 480                                     |

| DEC Single Density | IBM 3740<br>(IBM 1-128)<br>(#2305830)                              | 256,256                                       | 1                  | 77                      | 0                            | 128         | 128             | -               | 26          | 26              | -               | Yes              | Yes               | Yes                        | Yes                  | RX01,<br>IBM         | 5320 - System 32<br>5340 - System 34<br>5381 - System 38 |

| DEC Double Density | IBM 3740<br>(IBM 1-128<br>with set<br>media density)<br>(#2305830) | 512,512                                       | 1                  | 77                      | 0                            | 256         | 256             | -               | 26          | 26              | -               | Yes              | Yes               | Yes                        | Yes                  | RX02,<br>IBM         |                                                          |

| DEC Double Density | IBM 2-128<br>(with set<br>media density)<br>(#1766870)             | 1,205,024                                     | 2                  | 77                      | 0                            | 256         | 256             | 256             | 26          | 26              | 26              | No               | No                | Yes                        | Yes                  | RX02,<br>IBM         |                                                          |

| IBM Diskette 1     | IBM 1-128<br>(#2305830)                                            | 246,272                                       | 1                  | 74                      | 2                            | 128         | 128             | -               | 26          | 26              | -               | Yes              | Yes               | Yes                        | Yes                  | RX01,<br>IBM         | 5320 - System 32<br>5340 - System 34<br>5381 - System 38 |

| IBM Diskette 1     | IBM 1-256<br>(#2305845)                                            | 284,160                                       | 1                  | 74                      | 2                            | 256         | 128             | -               | 15          | 26              | -               | No               | No                | No                         | Yes                  | IBM                  | 5381 - System 38                                         |

| IBM Diskette 1     | IBM 1-512<br>(#1669954)                                            | 303,104                                       | 1                  | 74                      | 2                            | 512         | 128             | -               | 8           | 26              | -               | No               | No                | No                         | Yes                  | IBM                  | 5320 - System 32<br>5340 - System 34<br>5381 - System 38 |

| IBM Diskette 2     | IBM 2-128<br>(#1766870)                                            | 492,544                                       | 2                  | 74                      | 2                            | 128         | 128             | 128             | 26          | 26              | 26              | No               | No                | No                         | Yes                  | RX02,<br>IBM         | 5381 - System 38                                         |

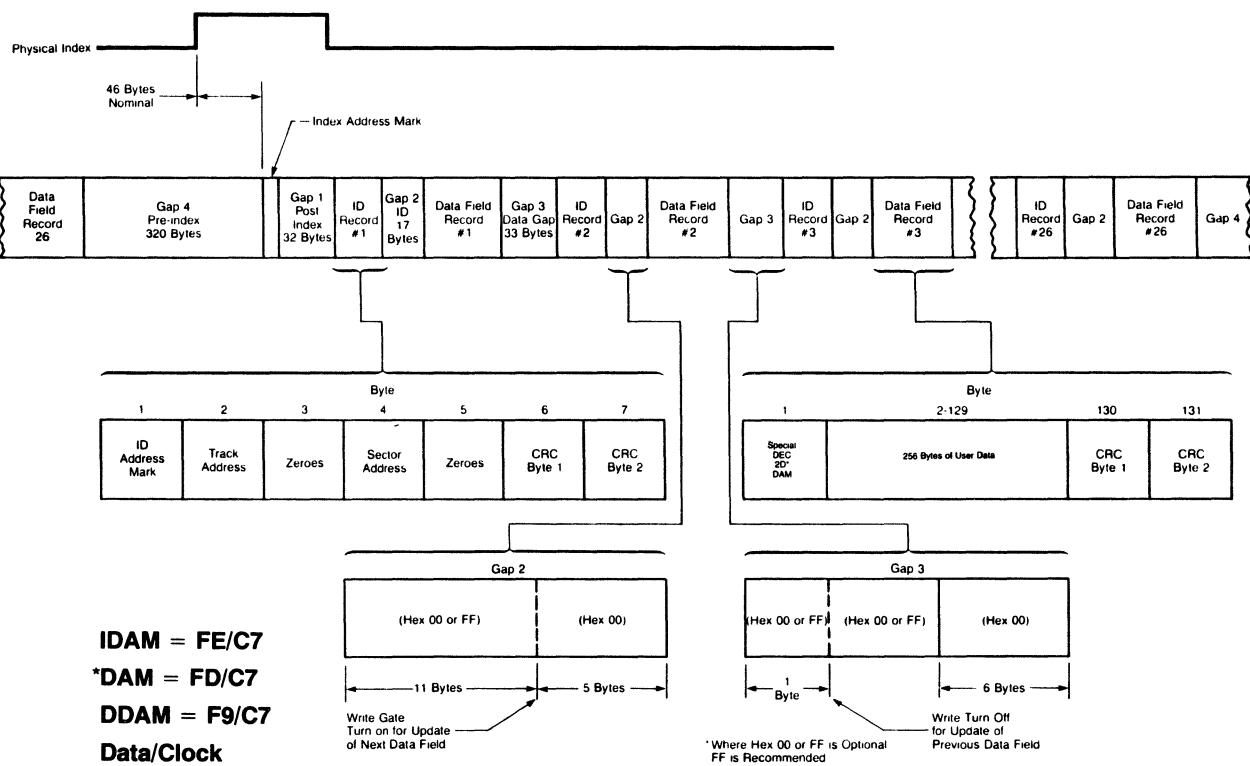

| IBM Diskette 2     | IBM 2-256<br>(#2736700)                                            | 568,320                                       | 2                  | 74                      | 2                            | 256         | 128             | 128             | 15          | 26              | 26              | No               | No                | No                         | Yes                  | IBM                  | 5381 - System 38                                         |

| IBM Diskette 2D    | IBM 2D-256<br>(#1766872)                                           | 985,088                                       | 2                  | 74                      | 2                            | 256         | 128             | 256             | 26          | 26              | 26              | No               | No                | No                         | Yes                  | RX02,<br>IBM         | 5340 - System 34<br>5381 - System 38                     |

| IBM Diskette 2D    | IBM 2D-512<br>(#1669044)                                           | 1,136,640                                     | 2                  | 74                      | 2                            | 512         | 128             | 256             | 15          | 26              | 26              | No               | No                | No                         | Yes                  | IBM                  | 5381 - System 38                                         |

| IBM Diskette 2D    | IBM 2D-1024<br>(#1669045)                                          | 1,212,416                                     | 2                  | 74                      | 2                            | 1024        | 128             | 256             | 8           | 26              | 26              | No               | No                | No                         | Yes                  | IBM                  | 5340 - System 34<br>5381 - System 38                     |

## DEC COMPATIBLE MODES

Modes 1 and 2 of the DSD 480 are fully DEC-compatible. Mode 2 (RX02 compatible) data transfers are done with DMA (direct memory access). Reading and writing is done in either single or double density. Mode 1 operation is single density only. Data transfer is by Programmed I/O.

## SINGLE SIDED OPERATION

Although the DSD 480 has double-sided disk drives, it will, of course, operate with single-sided diskettes. In fact, with single-sided diskettes, the DSD 480 provides a true emulation of the DEC RX02 (or RX01).

## DOUBLE SIDED OPERATION

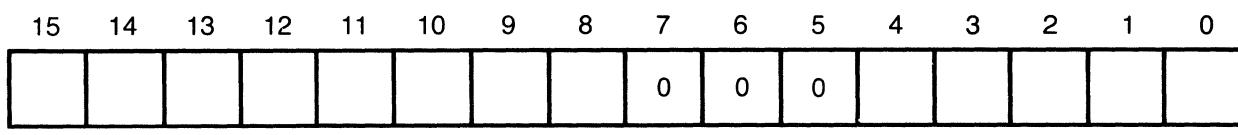

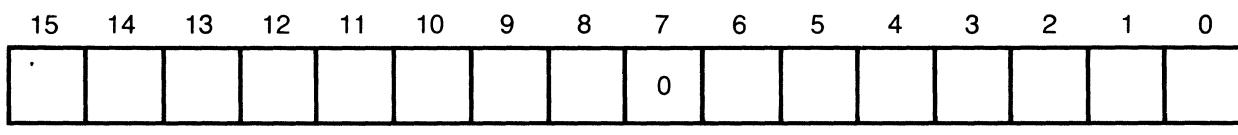

The DSD 480 allows the user to take full advantage of double capacity by activating double sided support in the DEC system monitor. Under double sided operation, bit 9 of the device COMMAND AND STATUS REGISTER (RXCS) is used to select diskette side 1 for reading or writing, and bit 1 of the ERROR AND STATUS REGISTER (RXES) is used to indicate "side 1 Ready".

The resulting RT-11 or RSX-11 monitor is fully DEC compatible. The operating system will function properly with DEC hardware (RX02) and all DEC utilities and applications programs. Appendix I describes the procedure for implementing double sided support in the DEC RT-11 and RSX-11 system monitors.

After double sided support has been installed in the monitor, the operating system will automatically check for the presence of double sided diskettes, and performs appropriate directory and housekeeping functions to make double or single sided operation fully software transparent. All system utilities (PIP, DUP, DIR, etc.) will function correctly with single or double sided diskettes.

For example, when a double sided diskette is initialized using "DUP" under RT-11, the monitor will recognize that the diskette is double sided. If the diskette is double density, there will be 1962 free blocks. If the disk is single density and double sided, there will be 974 free blocks.

If the user inserts a single sided diskette into the system, the monitor and floppy controller will recognize that the diskette is single sided and function properly.

## NOTE

Double sided diskettes will not function properly in a single sided drive.

## SINGLE DENSITY DISKETTES IN A DOUBLE DENSITY RX02-COMPATIBLE SYSTEM

The DSD 480 allows previously recorded single density file diskettes to be read and written by a double density operation system. The double density software device handler also reads and writes previously recorded single density diskettes. The expected density of a diskette is specified with the initial command sent by the device handler to the DSD 480. If the density of the diskette does not match the density specified in the command, the DSD 480 will report a density error to the device handler. In response, the handler will retransmit the command specifying the correct density. The entire operation is automatic, thus freeing you from manually checking each diskette to determine its density.

## IBM 2D-256 COMPATIBILITY IN MODE 2

While in RX02 mode, it is possible to read and write in IBM 2D-256 double density format, in the same fashion as a normal diskette. This allows the operator to exchange programs and data between DEC and IBM systems using the normal RX02 command structure.

As described earlier, IBM double density differs from DEC double density in that IBM sector headers and data are written in double density while DEC headers are single density and data are double density (Table 4-1). Note also that track 0 of an IBM 2D diskette is written in single density while the other 76 tracks are double density. This track is not normally used for data, and is not used by DEC RT-11 or RSX-11 software. Hence, it is possible to use an IBM 2D-256 diskette as a DEC system diskette. The procedure for generating a system diskette is described later.

The DSD 480 controller will automatically recognize the format of the diskette being used. IBM 2D-256 diskettes may be accessed with the standard DEC read and write calls or, if they contain a DEC operating system, they may be booted directly in the normal fashion.

## MODE 3

Mode 3 (Extended IBM) of the DSD 480 is an extension of Mode 2. It allows the user full compatibility with all DEC and IBM diskette formats. In addition, alternate track assignment is provided in a software transparent fashion. Mode 3 uses a special software device protocol which is described in this chapter. It is the user's responsibility to implement a device handler to support this protocol.

## PROGRAMMING INTERFACE

The system interface with the DSD 480 varies according to the host computer type and the operational mode for which the system is configured. The characteristics of the DSD 480 operation are embedded in the controller. A separate protocol for each mode is used to communicate with the interface module and host computer program.

The remainder of this chapter is organized by computer family and operational mode.

#### NOTE

All address locations and numerical machine values are represented in octal format.

### DEC 11 FAMILY

The system interface with the DSD 480 is identical for the LSI-11 and PDP-11.

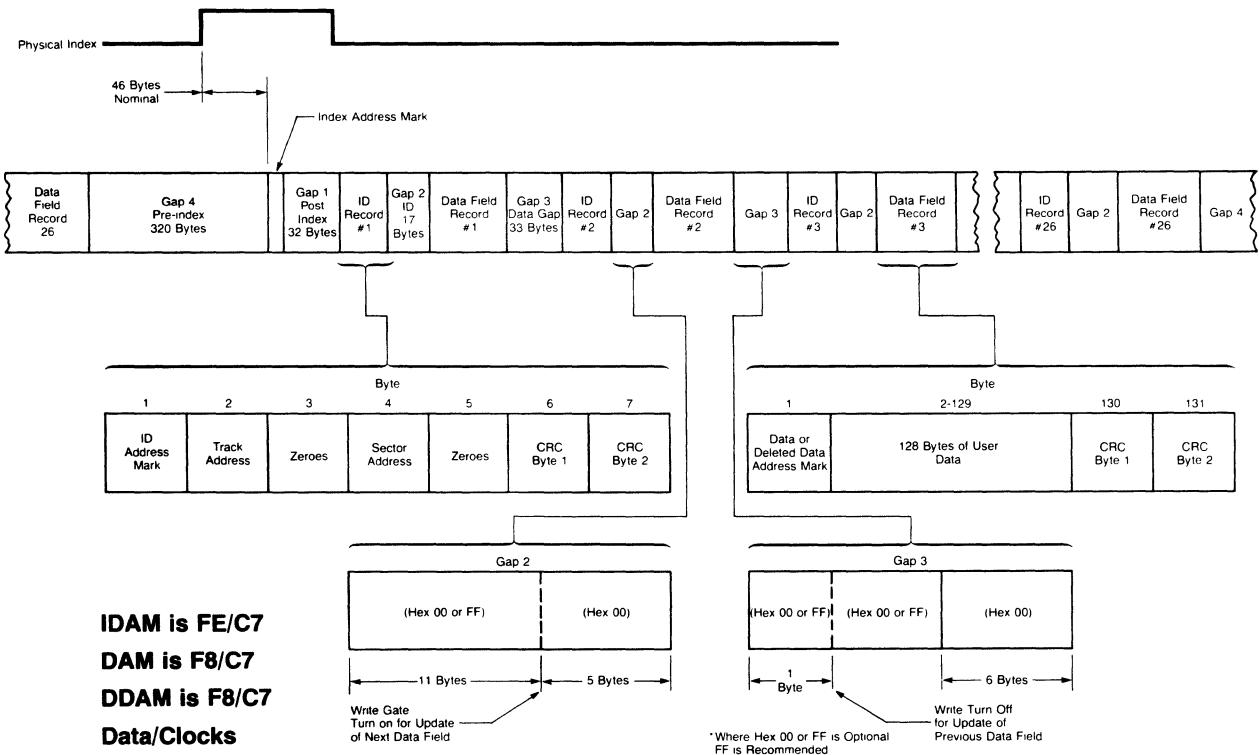

During Mode 1 (RX01 Compatible) or Mode 2 (RX02 Compatible) operation, data are transferred to and from the diskette in fixed length blocks called sectors. A sector contains 64 sixteen bit words when the system is being used in single density mode, and 128 sixteen bit words in double density mode. During Mode 3 (Extended IBM) operation, data are transferred in sectors of variable lengths.

The programmer can direct the DSD 480 controller to perform several operations or tasks. Each of these tasks is used to facilitate the storage and retrieval of information on a diskette.

As an example, two operations are needed to move a sector of data from main memory to a particular sector on a diskette. The first operation is called FILL BUFFER. This is used to move the data from computer memory to a RAM buffer which is an internal part of the disk controller. The second operation is called WRITE SECTOR. This positions the read/write head of a flexible disk drive over the specified portion of the diskette, and writes the data stored in the controller's sector buffer on the diskette.

The programmer communicates his task requirements to the DSD 480 controller through two physical registers which are addressed as though they were in computer memory. The CONTROL AND STATUS REGISTER is normally located at address 777170 octal. The DATA BUFFER REGISTER is normally located at address 777172 octal.

There are a total of seven "logical registers" that are mentioned throughout this chapter. These registers represent such information as data, controller status, track address and sector address. The programmer always reads and writes logical registers through the DATA BUFFER REGISTER, which is a physical register.

A task is initiated by writing a specific bit pattern to the CONTROL AND STATUS REGISTER. Each task is associated with a specific "protocol." A protocol is a set of rules which determine the parameters or data the computer should be passing through the DATA BUFFER REGISTER during the execution of a task.

For example, operations which move the read/write head in the disk drive require a track and sector address. The protocol for these functions is as follows:

- I) The command is written to the CONTROL AND STATUS REGISTER.

- 2) The sector address is written to the DATA BUFFER REGISTER when the controller requests it.

- 3) The track address is written to the DATA BUFFER REGISTER when the controller requests it.

The DSD 480 operational modes influence the protocol associated with the various tasks. The main difference in these modes centers on data transfer and storage characteristics. In Mode 1, programmed I/O is used exclusively for the transfer of both data and parameters between the computer and controller. In Modes 2 and Mode 3, programmed I/O is used to transfer parameters, but DMA is used to transfer data between the controller and main memory.

In Mode 1, data are recorded on a diskette in single density only. In Modes 2 and 3, data are recorded in either single density or double density.

### MODE 1 (RX01 COMPATIBLE) OPERATION

The system assumes MODE 1 operation when the "RX01" switch (located on the controller module) is placed in the "1" position and when the "ENRX01" jumper is installed on the PDP-11 or LSI-11 interface boards. Any program that runs successfully with the DSD 210, DSD 110, DSD 440 or the DEC RX-11 (or RXV-11) runs equally well on a DSD 480 system configured for operation in MODE 1.

### PERIPHERAL DEVICE REGISTERS

Programs communicate with the DSD 480 through two peripheral device registers. They are as follows:

| NAME | DESCRIPTION                 | OCTAL LOCATION |

|------|-----------------------------|----------------|

| RXCS | COMMAND AND STATUS REGISTER | 777170         |

| RXDB | DATA BUFFER REGISTER        | 777172         |

Peripheral device registers reside in the top 4K words of the DEC-11 family computers' memory address space. They are addressed as memory and any instruction that can operate on a memory location can operate on a peripheral device register in the same way. For information explaining how to assign non-standard bus addresses to these registers, see the section in Chapter 2 that describes installation of the interface module and cable.

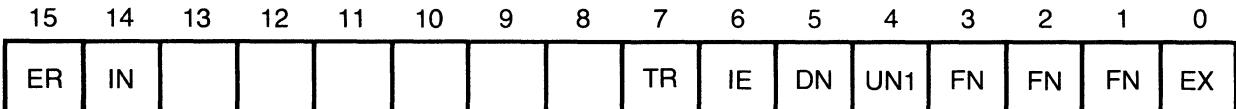

### COMMAND AND STATUS REGISTER (RXCS)

Writing bit patterns to this physical register controls the DSD 480. The format for this register is shown in Table 4-1. The RXCS register also provides important status information and error indications when read by the program.

## DATA BUFFER REGISTER (RXDB)

The RXDB, is physically a shift register that provides the communication link between the host processor and the DSD 480 system. The logical information passed through this physical register is based upon a predetermined protocol which is defined in the Mode I protocols section in this chapter.

If the DSD 480 is not in the process of executing a command, the RXDB can be written without risk. However, during the execution of an instruction, the RXDB register will only provide or accept information (according to the RXDB protocol) when the TRANSFER REQUEST flag is set.

### NOTE

Data may be lost if the correct protocol is not followed. Only RXDB bits 0-7 are accepted by the controller. Bits 8 through 15 are ignored.

The following descriptions explain the various logical register formats of the physical Data Buffer Register of RXDB.

### Data Buffer (RXDB)

The data buffer register is used by the function in process to transfer data to and from the controller data buffer. All information is transferred as a byte through bits 0-7 of the RXDB.

### Disk Track Address (RXTA)

At the proper time during commands requiring a track number (e.g. write sector, read sector), the track number is written to the physical RXDB register as if it were a logical register. This is the TRACK ADDRESS REGISTER (RXTA = 777172). Track numbers from 0-76 (decimal) are valid.

### Disk Sector Address (RXSA)

At the proper time during commands requiring a sector address (e.g. write sector, read sector) the sector address is written to the physical RXDB register as if it were a logical register. This is the SECTOR ADDRESS REGISTER (RXSA = 777172). Sector addresses from 1-26 (decimal) are valid. The controller microprocessor masks bits 6 and 7 of the RXSA to zeroes.

### System Error and Status Register (RXES)

The RXES is a logical register that is implemented using the physical RXDB shift register. It provides status and error information about the drive that has been selected in bit 4 of the physical RXCS register. At the completion of a command, the controller

places the RXES register into the data buffer register (RXDB = 777172) so that the host processor can check the status of the most recent operation.

#### BIT 7 - DRV RDY - Drive Ready

This bit, when set, indicates that the selected drive has a diskette installed correctly. The Drive Ready bit is only valid immediately following the Ready Status function. The bit is valid for drive 0 immediately following an initialize.

#### BIT 6 - DD - Deleted Data

This bit indicates that a deleted data address mark was found during the last READ SECTOR operation or that the last command was WRITE DELETED DATA SECTOR.

#### BIT 5 - DRV DEN - Drive Density

This bit indicates the density of the diskette installed in the selected drive. When asserted, double density is indicated. This bit is updated during READ or WRITE SECTOR operations.

#### BIT 4 - DEN ERR - Density Error

This bit indicates that during a READ or WRITE SECTOR operation, the controller found that the density of the selected diskette did not match the density given in the command. The operation is terminated and the ERROR and DONE bits are set.

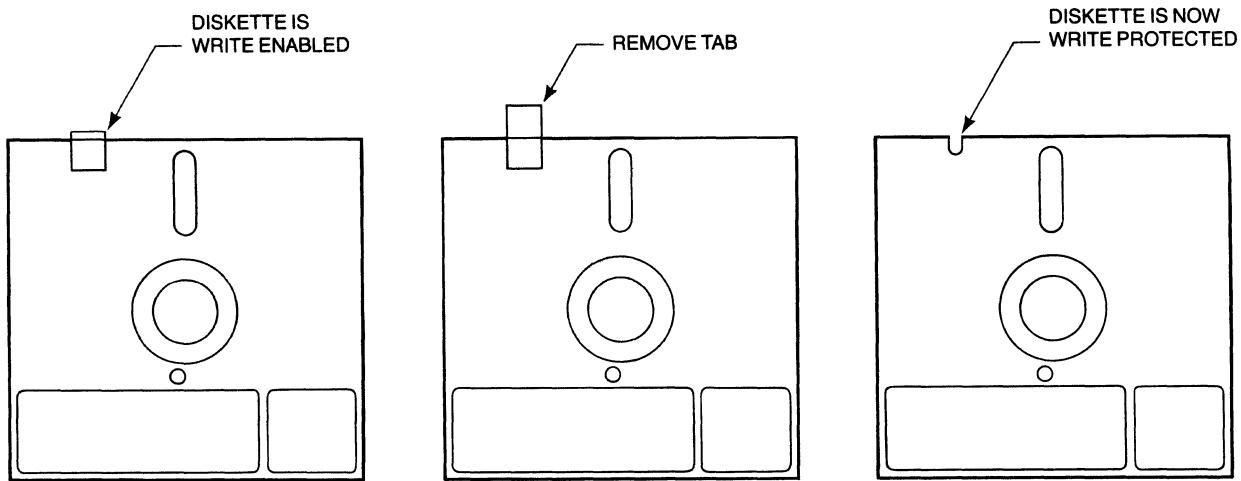

#### BIT 3 - WP - Write Protect (RX01 Mode only)

This bit is set whenever a write is attempted on a write-protected diskette. This RXDB bit along with the ERROR and DONE bits of the RXCS is set when the controller/drive subsystem loses power, or the IBUS cable is disconnected.

#### BIT 2 - ID - Initialize Done

This bit indicates that the controller/drive subsystem has just completed an initialization sequence. This sequence may have been started by a power failure, bus INIT, or programmed INIT.

#### BIT 1 - PAR - Parity Error

This bit indicates that a parity error was detected when a command or parameter was being shifted from the interface to the controller/drive subsystem. The operation is terminated; the ERROR and DONE bits are set.

#### BIT 0 - CRC - CRC Error

This bit indicates that a CRC (Cyclic Redundancy Check) Error was detected during the last Read sector operation. The operation is terminated; the ERROR and DONE bits are set.

The bit layout of this register is shown in Figure 4-1.

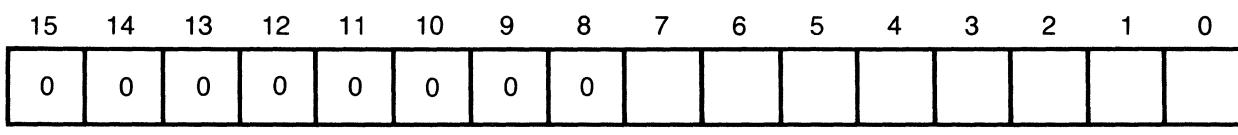

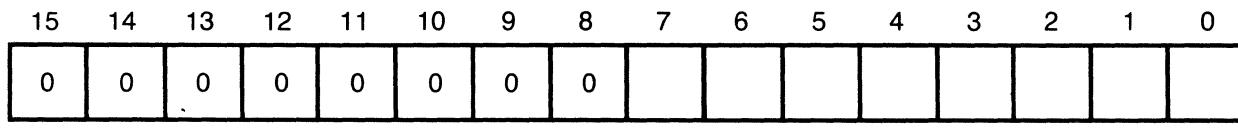

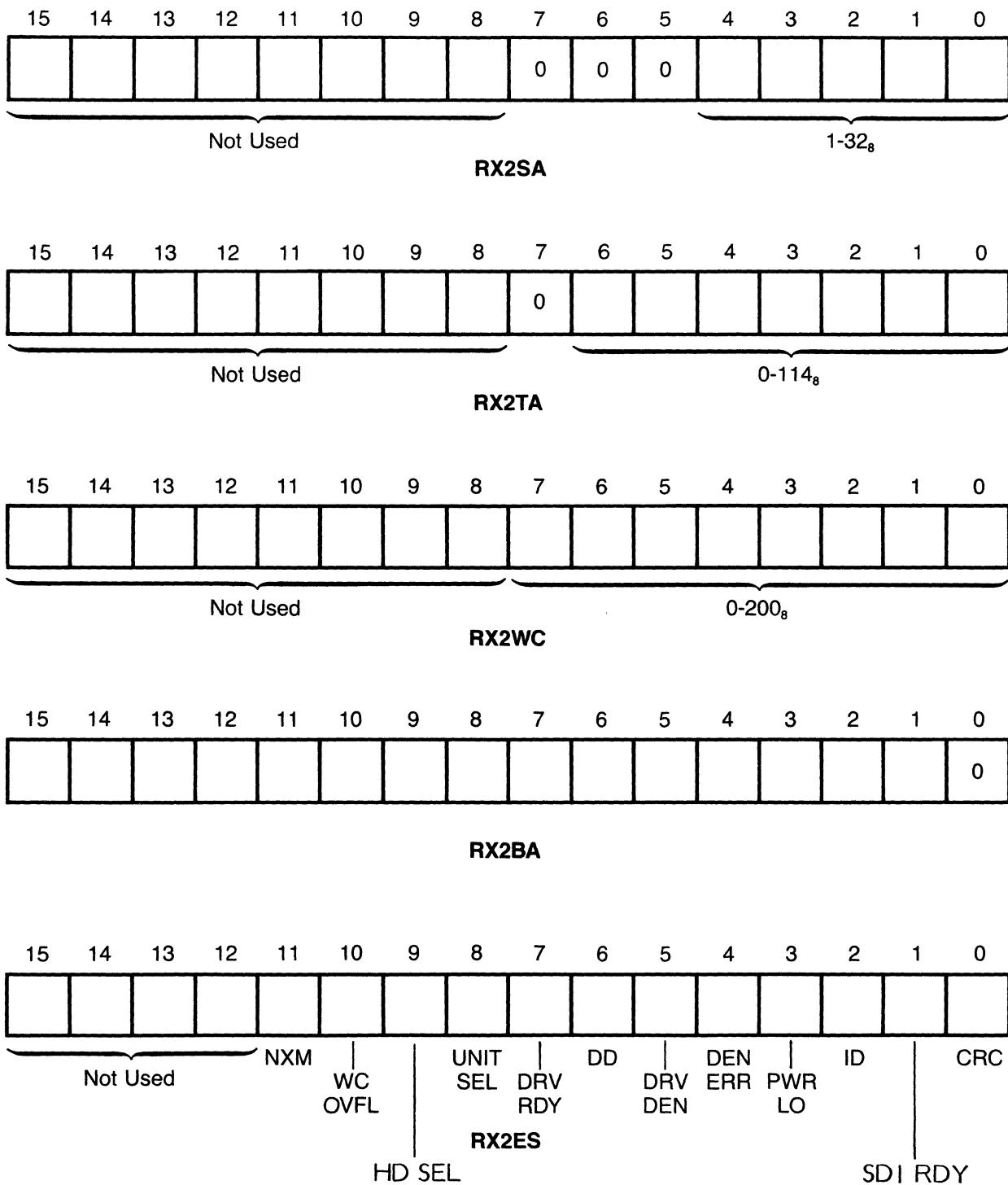

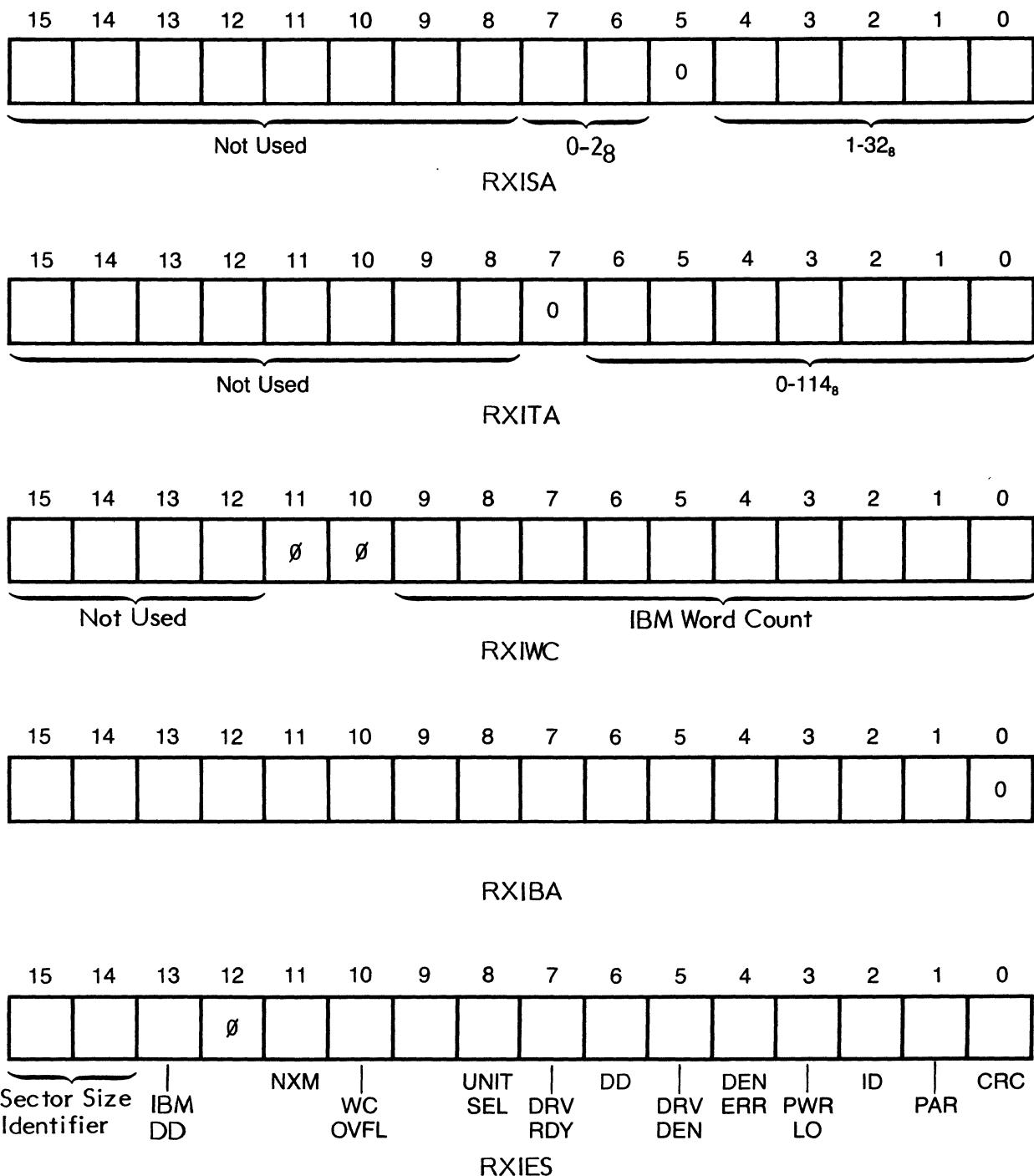

Table 4-2. Mode I Command and Status Register

Format for RXCS Register

| BIT  | MEANING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | ER — Error detected, cleared by INITIALIZE or new command. Read Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14   | IN — INITIALIZE the DSD 480. The DONE flag will be negated. the controller will self-test, drive 1 will seek to track 0, drive 0 will seek to track 0. A READ SECTOR operation on drive 0, track 1, sector 1 will occur if a diskette is in place; the ERROR AND STATUS REGISTER will be set to 0, the INITIALIZE DONE bit will be set in the ERROR AND STATUS REGISTER, and if drive 0 is ready, then the DRIVE READY bit will be set in the ERROR AND STATUS REGISTER. The INITIALIZE bit takes precedence over all other bits in the RXCS register. |

| 13-8 | UNUSED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7    | TR — TRANSFER REQUEST indicates to the program that the DATA BUFFER REGISTER has been emptied and needs loading or is loaded and needs emptying. Read only.                                                                                                                                                                                                                                                                                                                                                                                            |

| 6    | IE — INTERRUPT ENABLE permits an interrupt to occur when the DONE flag is set. It is a read/write bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5    | DN — DONE flag indicates the completion of an operation. The DONE flag is a read only bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5-4  | UN2 UN1 — Diskette drive unit select bits. The binary encoding of these bits selects drive 0-3. Drive selection only occurs if a drive related function is executed. A point of incompatibility exists when a triple or quad drive system is configured. DEC bootstraps assume that bit 5 is a "read only" bit, so they write into it with impunity. As a result, drive 2 is selected by mistake during bootstrapping. In systems configured for single or dual drive operation, bit 5 can be written into with impunity.                              |

| 3-1  | FN — FUNCTION SELECT <ul style="list-style-type: none"> <li>0 = FILL SECTOR BUFFER from memory</li> <li>1 = EMPTY SECTOR BUFFER into memory</li> <li>2 = WRITE SECTOR BUFFER to disk</li> <li>3 = READ SECTOR from disk to SECTOR BUFFER</li> <li>4 = Not used</li> <li>5 = READ STATUS (RXDB — RXES)</li> <li>6 = Write sector with deleted data address mark</li> <li>7 = READ ERROR REGISTER (RXDB — RXER)</li> </ul> Function select bits are write only.                                                                                          |

| 0    | EX — Execute, when set, causes the function coded in RXCS bits 3-1 to be executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Not Used

Read/Write These Bits Only

**RXDB**

Not Used

$1-32_8$

**RXSA**

Not Used

$0-114_8$

**RXTA**

Not Used

Error Code

**RXER**

Not Used

DD | DRV RDY      DEN | DRV DEN      PWR LO | ID | PAR | CRC

**RXES**

Figure 4-1. Mode 1 Register Formats

### Error Register (RXER)

The RXER is a logical register that is implemented using the RXDB shift register. It contains a definitive code identifying an error condition. The RXER is available only after the "Read Error Register" command (111). At the completion of this command, the controller places the contents of the RXER into the data buffer so that the host processor may read the definitive error code.

Bits 15-8: Not Used

Bits 7-0: Definitive Error Code

Refer to Table 4-3

### MODE I PROTOCOLS